Steven F. Barrett, Daniel J. Pack

Microcontroller Programming and Interfacing with Texas Instruments MSP430FR2433 and MSP430FR5994

Second Edition

Synthesis Lectures on Digital Circuits and Systems

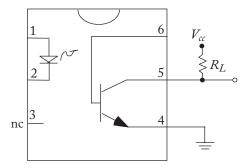

Mitchell A. Thornton, Series Editor

Microcontroller Programming and Interfacing with Texas Instruments MSP430FR2433 and MSP430FR5994 Second Edition

# Synthesis Lectures on Digital Circuits and Systems

### Editor Mitchell A. Thornton, Southern Methodist University

The Synthesis Lectures on Digital Circuits and Systems series is comprised of 50- to 100-page books targeted for audience members with a wide-ranging background. The Lectures include topics that are of interest to students, professionals, and researchers in the area of design and analysis of digital circuits and systems. Each Lecture is self-contained and focuses on the background information required to understand the subject matter and practical case studies that illustrate applications. The format of a Lecture is structured such that each will be devoted to a specific topic in digital circuits and systems rather than a larger overview of several topics such as that found in a comprehensive handbook. The Lectures cover both well-established areas as well as newly developed or emerging material in digital circuits and systems design and analysis.

Microcontroller Programming and Interfacing with Texas Instruments MSP430FR2433 and MSP430FR5994, Second Edition

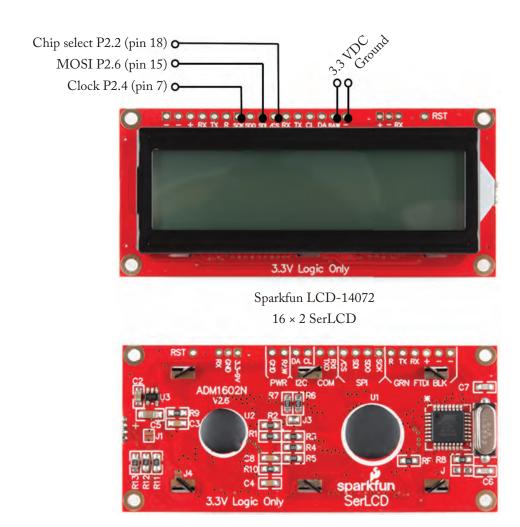

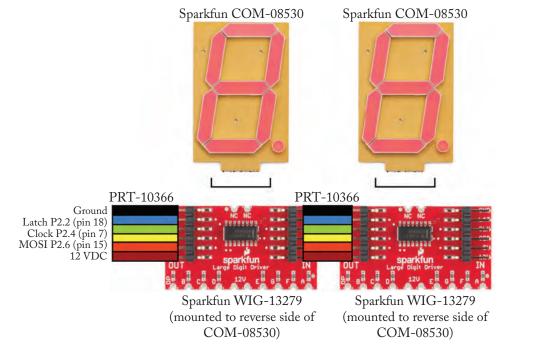

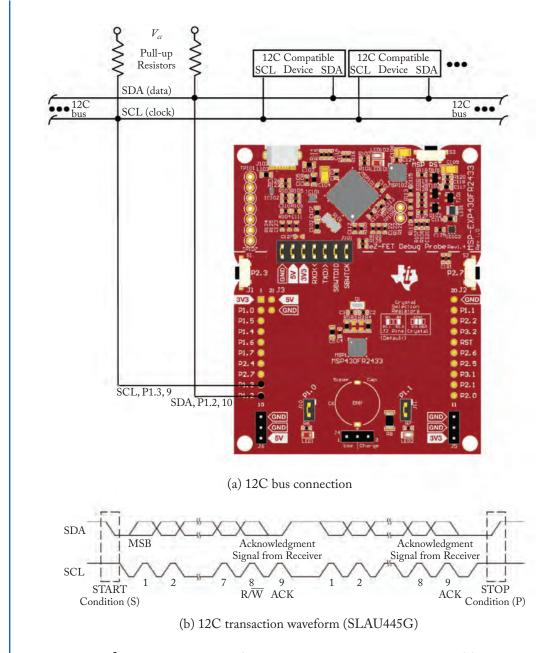

Steven F. Barrett and Daniel J. Pack 2019

Synthesis of Quantum Circuits vs. Synthesis of Classical Reversible Circuits Alexis De Vos, Stijn De Baerdemacker, and Yvan Van Rentergen 2018

Boolean Differential Calculus Bernd Steinbach and Christian Posthoff 2017

Embedded Systems Design with Texas Instruments MSP432 32-bit Processor Dung Dang, Daniel J. Pack, and Steven F. Barrett 2016

Fundamentals of Electronics: Book 4 Oscillators and Advanced Electronics Topics Thomas F. Schubert and Ernest M. Kim 2016

Fundamentals of Electronics: Book 3 Active Filters and Amplifier Frequency Thomas F. Schubert and Ernest M. Kim 2016 Bad to the Bone: Crafting Electronic Systems with BeagleBone and BeagleBone Black, Second Edition

Steven F. Barrett and Jason Kridner 2015

Fundamentals of Electronics: Book 2 Amplifiers: Analysis and Design Thomas F. Schubert and Ernest M. Kim 2015

Fundamentals of Electronics: Book 1 Electronic Devices and Circuit Applications Thomas F. Schubert and Ernest M. Kim 2015

Applications of Zero-Suppressed Decision Diagrams Tsutomu Sasao and Jon T. Butler 2014

Modeling Digital Switching Circuits with Linear Algebra Mitchell A. Thornton 2014

Arduino Microcontroller Processing for Everyone! Third Edition Steven F. Barrett 2013

Boolean Differential Equations Bernd Steinbach and Christian Posthoff 2013

Bad to the Bone: Crafting Electronic Systems with BeagleBone and BeagleBone Black Steven F. Barrett and Jason Kridner 2013

Introduction to Noise-Resilient Computing S.N. Yanushkevich, S. Kasai, G. Tangim, A.H. Tran, T. Mohamed, and V.P. Shmerko 2013

Atmel AVR Microcontroller Primer: Programming and Interfacing, Second Edition Steven F. Barrett and Daniel J. Pack 2012

Representation of Multiple-Valued Logic Functions Radomir S. Stankovic, Jaakko T. Astola, and Claudio Moraga 2012

Arduino Microcontroller: Processing for Everyone! Second Edition Steven F. Barrett 2012 iv

| iv     |                                                                                                                                                     |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| I      | Advanced Circuit Simulation Using Multisim Workbench<br>David Báez-López, Félix E. Guerrero-Castro, and Ofelia Delfina Cervantes-Villagómez<br>2012 |

| I      | Circuit Analysis with Multisim<br>David Báez-López and Félix E. Guerrero-Castro<br>2011                                                             |

| S      | Microcontroller Programming and Interfacing Texas Instruments MSP430, Part I<br>Steven F. Barrett and Daniel J. Pack<br>2011                        |

| S      | Microcontroller Programming and Interfacing Texas Instruments MSP430, Part II<br>Steven F. Barrett and Daniel J. Pack<br>2011                       |

| I      | Pragmatic Electrical Engineering: Systems and Instruments<br>William Eccles<br>2011                                                                 |

| I      | Pragmatic Electrical Engineering: Fundamentals<br>William Eccles<br>2011                                                                            |

| ]<br>] | ntroduction to Embedded Systems: Using ANSI C and the Arduino Development<br>Environment<br>David J. Russell<br>2010                                |

| S      | Arduino Microcontroller: Processing for Everyone! Part II<br>Steven F. Barrett<br>2010                                                              |

| S      | Arduino Microcontroller Processing for Everyone! Part I<br>Steven F. Barrett<br>2010                                                                |

| Ι      | Digital System Verification: A Combined Formal Methods and Simulation Framework<br>Lun Li and Mitchell A. Thornton<br>2010                          |

|        | Progress in Applications of Boolean Functions<br>Isutomu Sasao and Jon T. Butler<br>2009                                                            |

| S      | Embedded Systems Design with the Atmel AVR Microcontroller: Part II<br>Steven F. Barrett<br>2009                                                    |

Embedded Systems Design with the Atmel AVR Microcontroller: Part I Steven F. Barrett 2009

Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller II: Digital and Analog Hardware Interfacing

v

Douglas H. Summerville 2009

Designing Asynchronous Circuits using NULL Convention Logic (NCL) Scott C. Smith and JiaDi 2009

Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller I: Assembly Language Programming Douglas H.Summerville 2009

Developing Embedded Software using DaVinci & OMAP Technology B.I. (Raj) Pawate 2009

Mismatch and Noise in Modern IC Processes Andrew Marshall 2009

Asynchronous Sequential Machine Design and Analysis: A Comprehensive Development of the Design and Analysis of Clock-Independent State Machines and Systems Richard F. Tinder 2009

An Introduction to Logic Circuit Testing Parag K. Lala 2008

Pragmatic Power William J. Eccles 2008

Multiple Valued Logic: Concepts and Representations D. Michael Miller and Mitchell A. Thornton 2007

Finite State Machine Datapath Design, Optimization, and Implementation Justin Davis and Robert Reese 2007 vi

Atmel AVR Microcontroller Primer: Programming and Interfacing Steven F. Barrett and Daniel J. Pack 2007

Pragmatic Logic William J. Eccles 2007

PSpice for Filters and Transmission Lines Paul Tobin 2007

PSpice for Digital Signal Processing Paul Tobin 2007

PSpice for Analog Communications Engineering Paul Tobin 2007

PSpice for Digital Communications Engineering Paul Tobin 2007

PSpice for Circuit Theory and Electronic Devices Paul Tobin 2007

Pragmatic Circuits: DC and Time Domain William J. Eccles 2006

Pragmatic Circuits: Frequency Domain William J. Eccles 2006

Pragmatic Circuits: Signals and Filters William J. Eccles 2006

High-Speed Digital System Design Justin Davis 2006

Introduction to Logic Synthesis using Verilog HDL Robert B.Reese and Mitchell A.Thornton 2006 Microcontrollers Fundamentals for Engineers and Scientists Steven F. Barrett and Daniel J. Pack 2006 Copyright © 2019 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

Microcontroller Programming and Interfacing with Texas Instruments MSP430FR2433 and MSP430FR5994, Second Edition

Steven F. Barrett and Daniel J. Pack

www.morganclaypool.com

| ISBN: 9781681736242 | paperback |

|---------------------|-----------|

| ISBN: 9781681736273 | hardcover |

A Publication in the Morgan & Claypool Publishers series SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS

Lecture #54 Series Editor: Mitchell A. Thornton, *Southern Methodist University* Series ISSN Print 1932-3166 Electronic 1932-3174

# Microcontroller Programming and Interfacing with Texas Instruments MSP430FR2433 and MSP430FR5994

## **Second Edition**

Steven F. Barrett University of Wyoming, Laramie, WY

Daniel J. Pack University of Tennessee Chattanooga, TN

SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS #54

MORGAN & CLAYPOOL PUBLISHERS

## ABSTRACT

This book provides a thorough introduction to the Texas Instruments MSP430<sup>TM</sup> microcontroller. The MSP430 is a 16-bit reduced instruction set (RISC) processor that features ultra-low power consumption and integrated digital and analog hardware. Variants of the MSP430 microcontroller have been in production since 1993. This provides for a host of MSP430 products including evaluation boards, compilers, software examples, and documentation. A thorough introduction to the MSP430 line of microcontrollers, programming techniques, and interface concepts are provided along with considerable tutorial information with many illustrated examples. Each chapter provides laboratory exercises to apply what has been presented in the chapter. The book is intended for an upper level undergraduate course in microcontrollers or mechatronics but may also be used as a reference for capstone design projects. Also, practicing engineers already familiar with another microcontroller, who require a quick tutorial on the microcontroller, will find this book very useful. This second edition introduces the MSP–EXP430FR5994 and the MSP430–EXP430FR2433 LaunchPads. Both LaunchPads are equipped with a variety of peripherals and Ferroelectric Random Access Memory (FRAM). FRAM is a nonvolatile, lowpower memory with functionality similar to flash memory.

## **KEYWORDS**

MSP430 microcontroller, microcontroller interfacing, embedded systems design, Texas Instruments

To our families

# Contents

| Preface |       |                                                                           |  |

|---------|-------|---------------------------------------------------------------------------|--|

|         | Ackr  | nowledgments xxix                                                         |  |

| 1       | Intro | oduction to Microcontroller Technology1                                   |  |

|         | 1.1   | Motivation                                                                |  |

|         | 1.2   | Background Theory: A Brief History and Terminology                        |  |

|         | 1.3   | Microcontroller Systems                                                   |  |

|         | 1.4   | Why the Texas Instruments MSP430?                                         |  |

|         | 1.5   | Target Microcontroller Features    5                                      |  |

|         | 1.6   | Introduction to the Evaluation Modules (EVM) 11                           |  |

|         | 1.7   | Development Software                                                      |  |

|         | 1.8   | Lab 1: Getting Acquainted with Hardware and Software Development<br>Tools |  |

|         | 1.9   | Summary                                                                   |  |

|         | 1.10  | References and Further Reading                                            |  |

|         | 1.11  | Chapter Problems                                                          |  |

| 2       | A Br  | ief Introduction to Programming21                                         |  |

|         | 2.1   | Overview                                                                  |  |

|         | 2.2   | Energia                                                                   |  |

|         | 2.3   | Energia Quickstart                                                        |  |

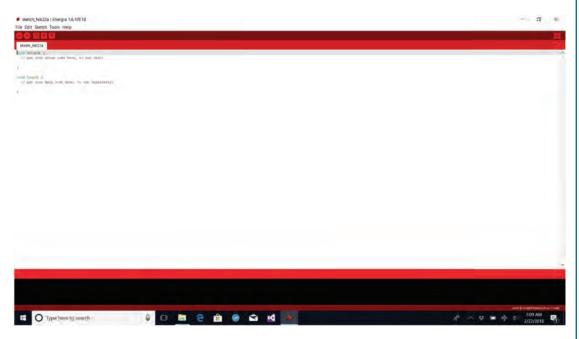

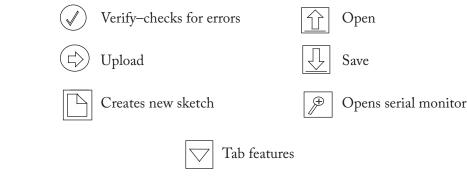

|         | 2.4   | Energia Development Environment                                           |  |

|         |       | 2.4.1 Energia IDE Overview                                                |  |

|         |       | 2.4.2 Sketchbook Concept                                                  |  |

|         |       | 2.4.3 Energia Software, Libraries, and Language References 24             |  |

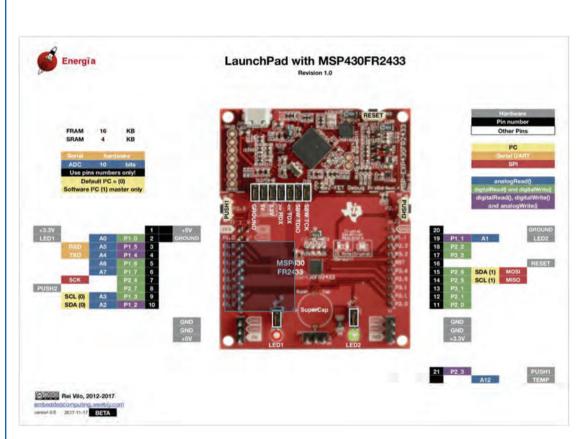

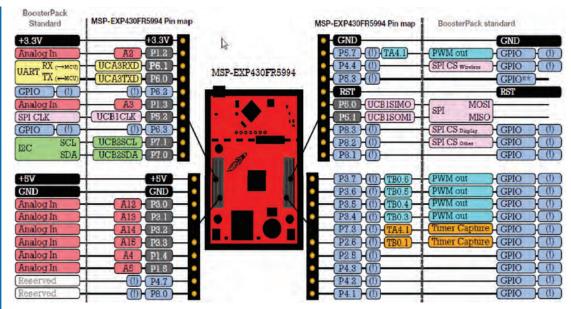

|         | 2.5   | Energia Pin Assignments                                                   |  |

|         | 2.6   | Writing an Energia Sketch                                                 |  |

|         |       | 2.6.1 Control Algorithm for the Mini Round Robot                          |  |

|         | 2.7   | Some Additional Comments on Energia                                       |  |

|         | 2.8   | Programming in C                                                          |  |

| XIV |      |                                                            |

|-----|------|------------------------------------------------------------|

|     | 2.9  | Anatomy of a Program                                       |

|     |      | 2.9.1 Comments                                             |

|     |      | 2.9.2 Include Files                                        |

|     |      | 2.9.3 Functions                                            |

|     |      | 2.9.4 Port Configuration 59                                |

|     |      | 2.9.5 Program Constants                                    |

|     |      | 2.9.6 Interrupt Handler Definitions                        |

|     |      | 2.9.7 Variables                                            |

|     |      | 2.9.8 Main Program                                         |

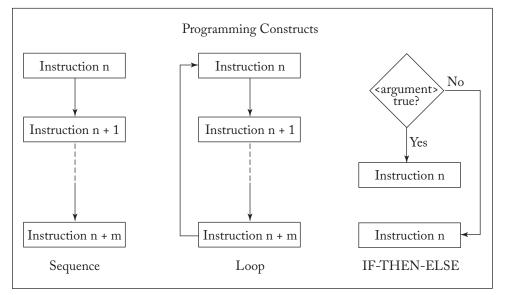

|     | 2.10 | Fundamental Programming Concepts                           |

|     |      | 2.10.1 Operators                                           |

|     |      | 2.10.2 Programming Constructs                              |

|     |      | 2.10.3 Decision Processing                                 |

|     | 2.11 | Laboratory Exercise: Getting Acquainted with Energia and C |

|     | 2.12 | Summary                                                    |

|     | 2.13 | References and Further Reading                             |

|     | 2.14 | Chapter Problems                                           |

| 2   | Uand | hunge Organization and Software Decomposing 91             |

| 3   |      | Iware Organization and Software Programming         81     |

|     | 3.1  | Motivation                                                 |

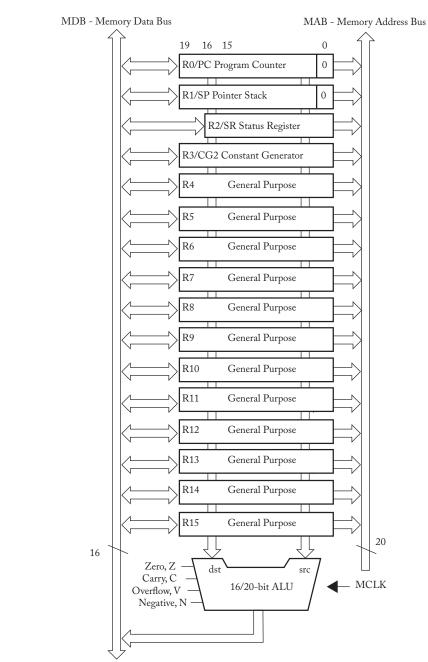

|     | 3.2  | MSP430 Hardware Organization/Architecture                  |

|     |      | 3.2.1 Chip Organization                                    |

|     |      | 3.2.2 Hardware Pin Assignments                             |

|     | 3.3  | Hardware Subsystems                                        |

|     |      | 3.3.1 Register Block                                       |

|     |      | 3.3.2 Port System                                          |

|     |      | 3.3.3 Timer System                                         |

|     |      | 3.3.4 Memory System                                        |

|     |      | 3.3.5 Resets and Interrupts                                |

|     |      | 3.3.6 Communication Systems                                |

|     |      | 3.3.7 Analog-to-Digital Converter                          |

|     |      | 3.3.8 Hardware Multiplier (MPY32) 90                       |

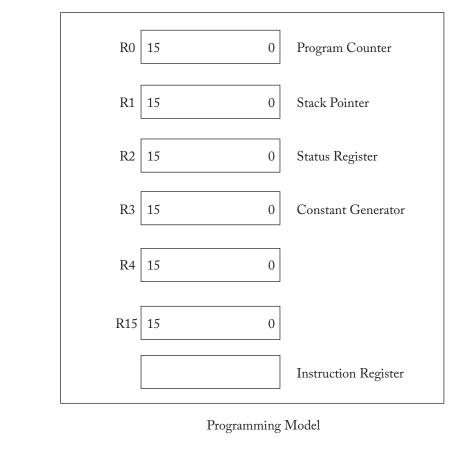

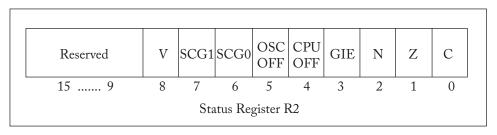

|     | 3.4  | CPU Programming Model/Register Descriptions                |

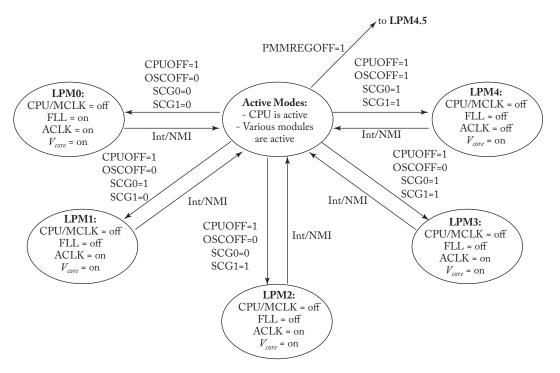

|     | 3.5  | Operating Modes                                            |

|     | 3.6  | Software Programming 100                                   |

|     |      | 3.6.1 MSP430 Assembly Language 101                         |

|     |      | 3.6.2 Directives                                           |

xiv

|   |      | 3.6.3   | Assembly Process                                                   | 1 |

|---|------|---------|--------------------------------------------------------------------|---|

|   |      | 3.6.4   | Instruction Set Architecture                                       | ) |

|   | 3.7  | Addres  | sing Modes                                                         | ) |

|   |      | 3.7.1   | Register Addressing Mode 119                                       | ) |

|   |      | 3.7.2   | Indexed Addressing Mode 119                                        |   |

|   |      | 3.7.3   | Symbolic Addressing Mode 121                                       |   |

|   |      | 3.7.4   | Absolute Addressing Mode 121                                       |   |

|   |      | 3.7.5   | Indirect Register Addressing Mode 121                              |   |

|   |      | 3.7.6   | Indirect Autoincrement Addressing Mode 121                         |   |

|   |      | 3.7.7   | Immediate Addressing Mode 121                                      |   |

|   |      | 3.7.8   | Programming Constructs 122                                         | 1 |

|   |      | 3.7.9   | Orthogonal Instruction Set 123                                     | , |

|   | 3.8  | Softwa  | re Programming Skills 124                                          | ł |

|   | 3.9  | Asseml  | oly vs. C                                                          |   |

|   |      | 3.9.1   | Our Approach                                                       |   |

|   | 3.10 | Accessi | ing and Debugging Tools 128                                        | 5 |

|   | 3.11 | Labora  | tory Exercise: Programming the MSP430 in Assembly Language 128     | 5 |

|   |      | 3.11.1  | Part 1: Flash an LED via Assembly Language 128                     | 5 |

|   |      |         | Part 2: Illuminate a LED via Assembly Language 132                 |   |

|   |      | 3.11.3  | Part 3: Mathematical Operations in Assembly Language 134           | ł |

|   | 3.12 | Summa   | ary                                                                |   |

|   | 3.13 | Referen | nces and Further Reading 135                                       |   |

|   | 3.14 | Chapte  | r Problems                                                         | ) |

| 4 | MSP  | 430 Op  | erating Parameters and Interfacing139                              | ) |

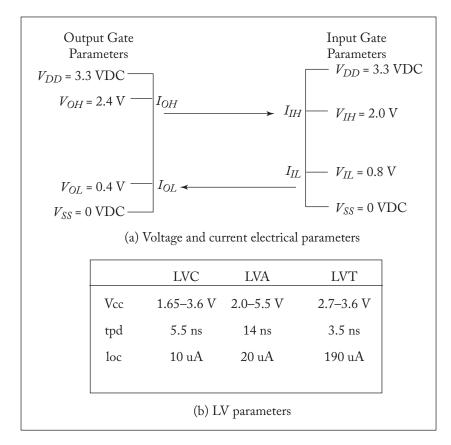

| - | 4.1  | -       | ing Parameters                                                     |   |

|   |      | 4.1.1   | MSP430 3.3 VDC operation                                           |   |

|   |      | 4.1.2   | Compatible 3.3 VDC Logic Families                                  |   |

|   |      | 4.1.3   | Microcontroller Operation at 5.0 VDC                               |   |

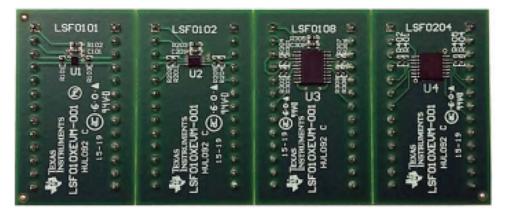

|   |      | 4.1.4   | Interfacing 3.3 VDC Logic Devices with 5.0 VDC Logic Families. 144 |   |

|   | 4.2  |         | Devices                                                            |   |

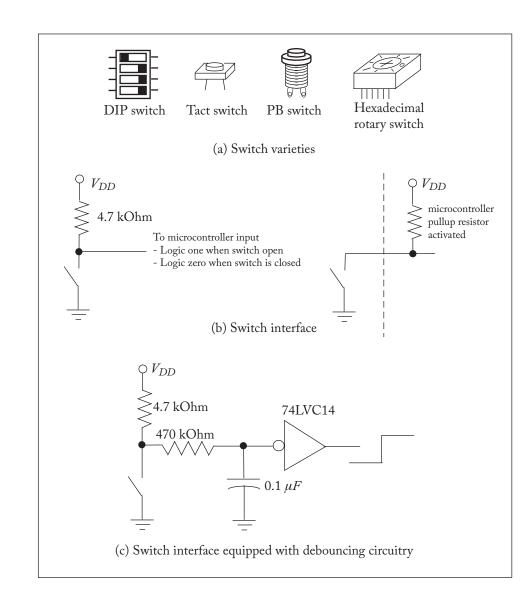

|   |      | 4.2.1   | Switches                                                           |   |

|   |      | 4.2.2   | Switch Debouncing                                                  |   |

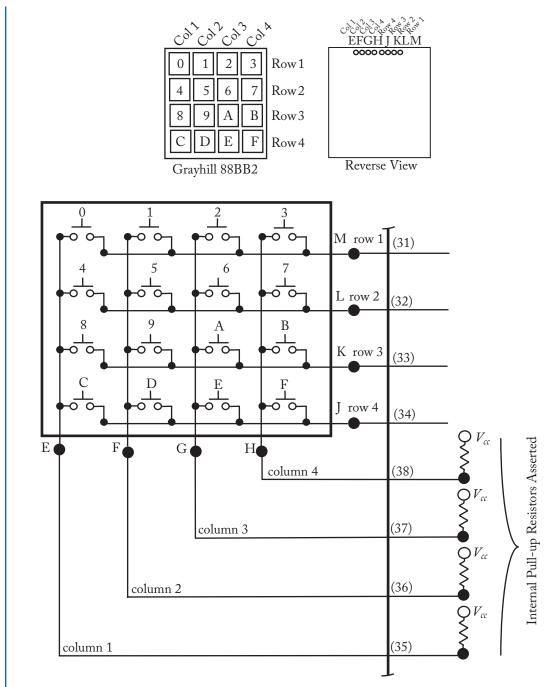

|   |      | 4.2.3   | Keypads                                                            |   |

|   |      | 4.2.4   | Sensors                                                            |   |

|   |      | 4.2.5   | Transducer Interface Design (TID) Circuit                          |   |

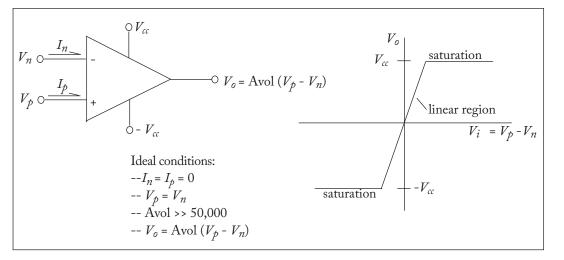

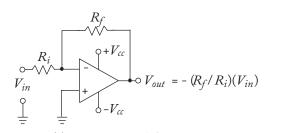

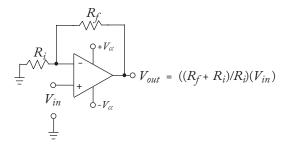

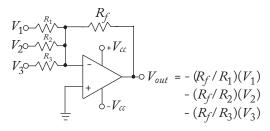

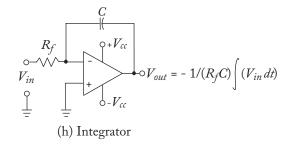

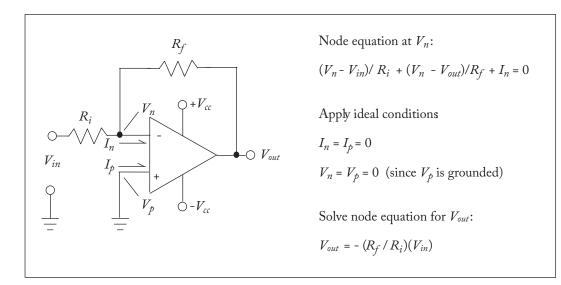

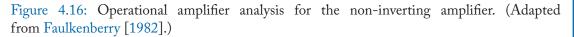

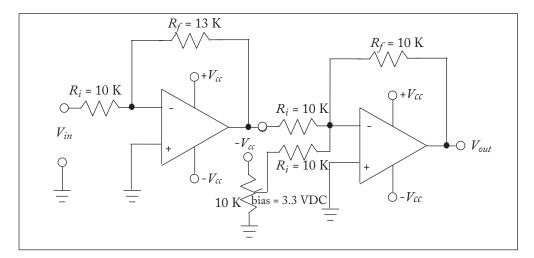

|   |      | 4.2.6   | Operational Amplifiers                                             |   |

xv

| V | 171 |

|---|-----|

| А | V 1 |

|   |     |

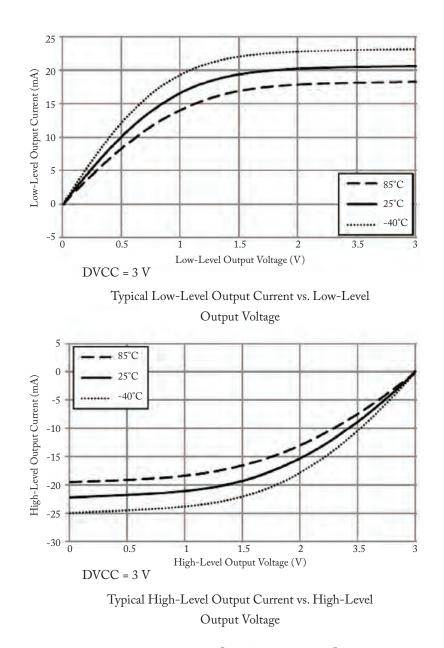

|   | 4.3   | Output Devices                                                         | . 165 |

|---|-------|------------------------------------------------------------------------|-------|

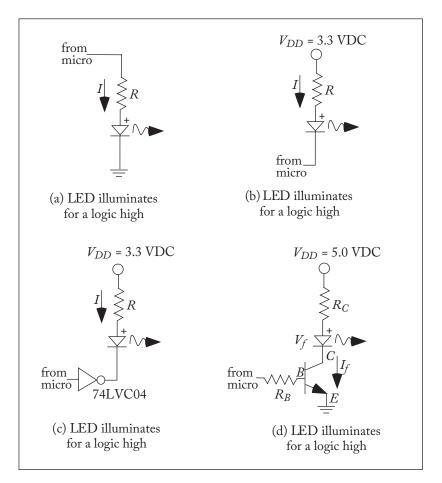

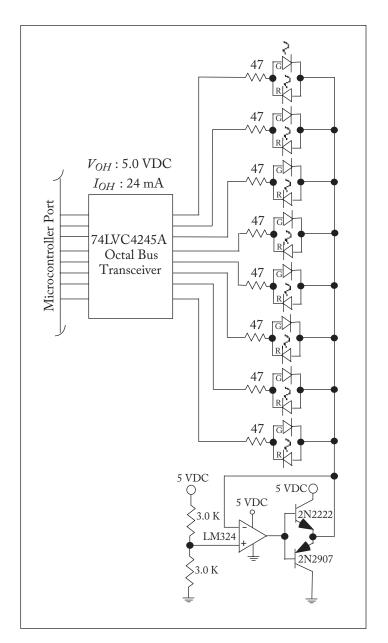

|   |       | 4.3.1 Light-Emitting Diodes (LEDs)                                     | . 168 |

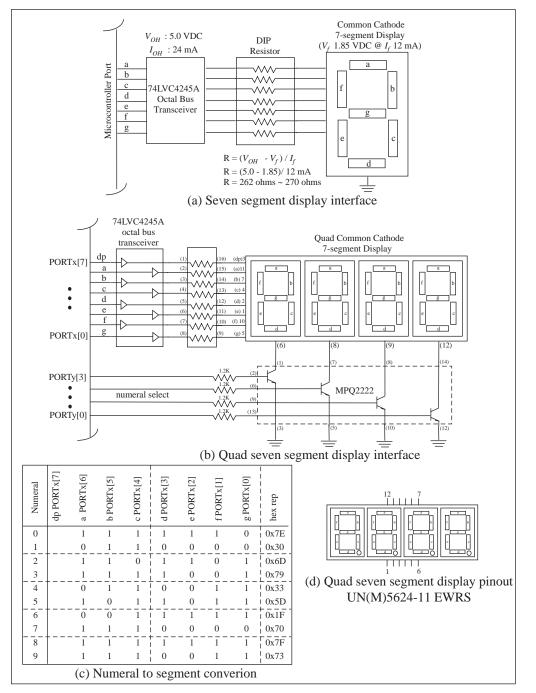

|   |       | 4.3.2 Seven-Segment LED Displays                                       | . 170 |

|   |       | 4.3.3 Tri-State LED Indicator                                          | . 172 |

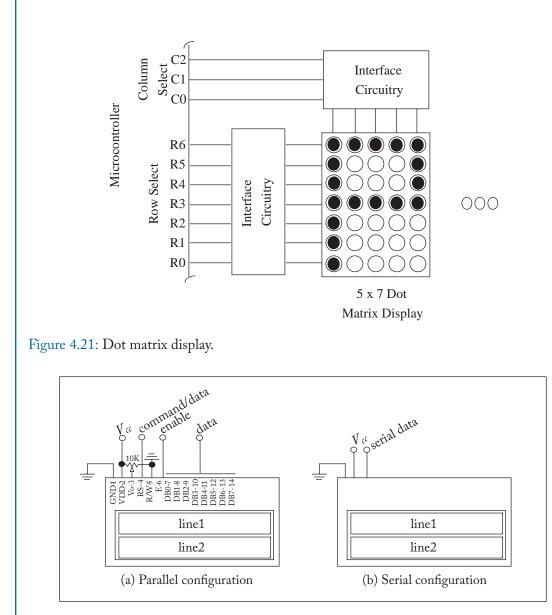

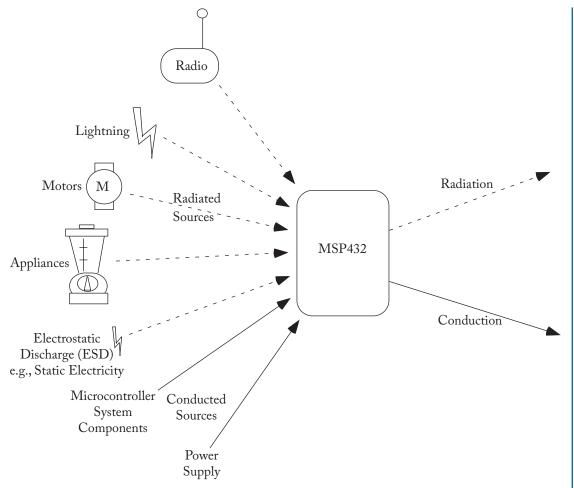

|   |       | 4.3.4 Dot Matrix Display                                               | . 172 |

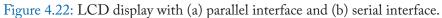

|   |       | 4.3.5 Liquid Crystal Display (LCD)                                     | . 172 |

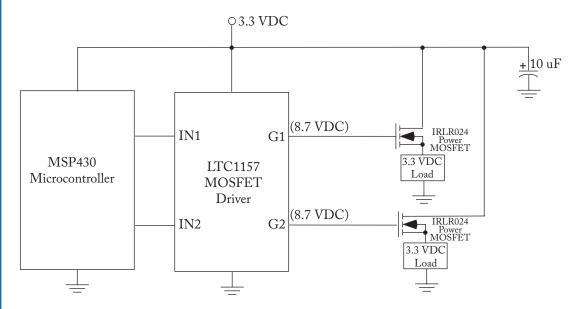

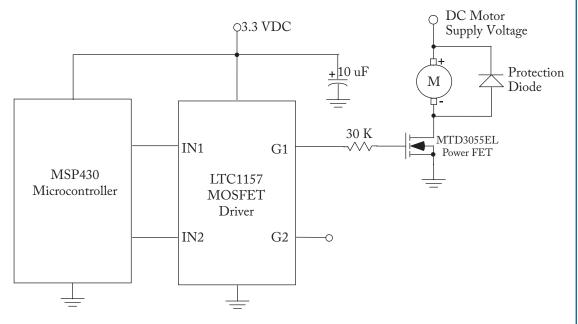

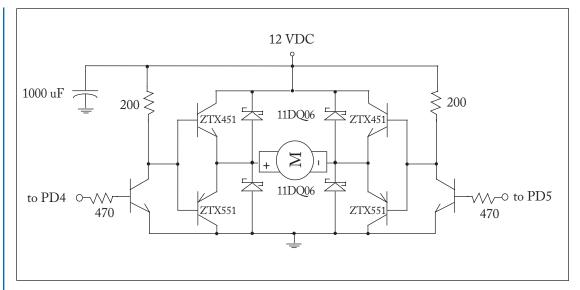

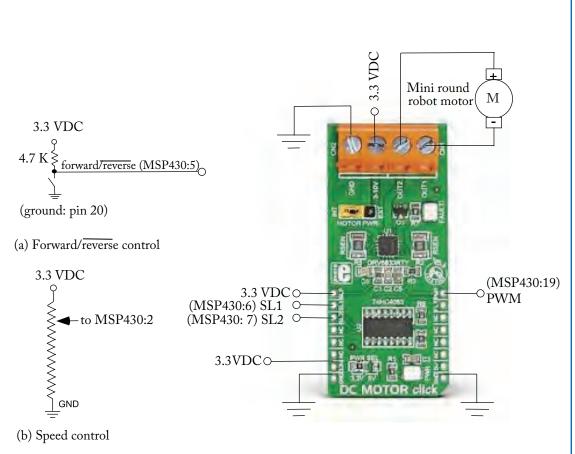

|   | 4.4   | High-Power DC Interfaces                                               | . 176 |

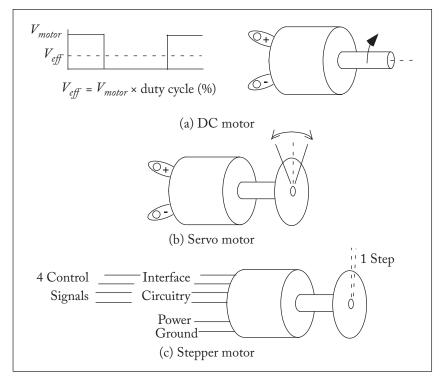

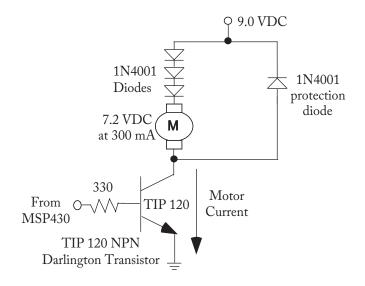

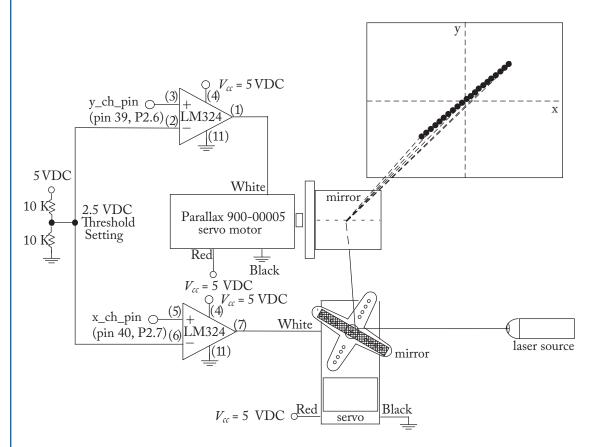

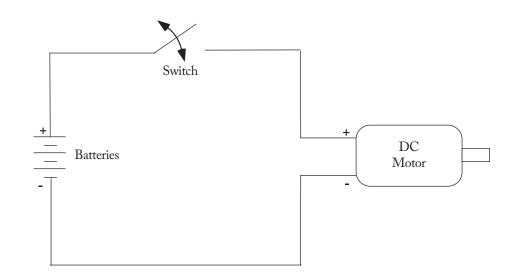

|   |       | 4.4.1 DC Motor Interface, Speed, and Direction Control                 | . 180 |

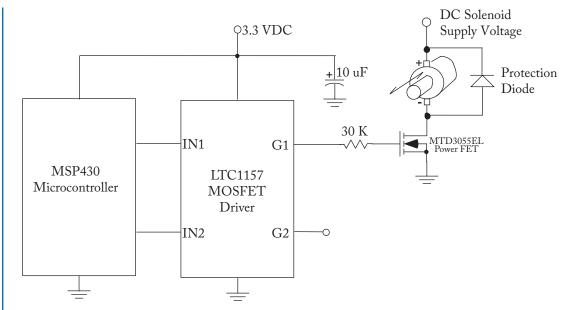

|   |       | 4.4.2 DC Solenoid Control                                              | . 185 |

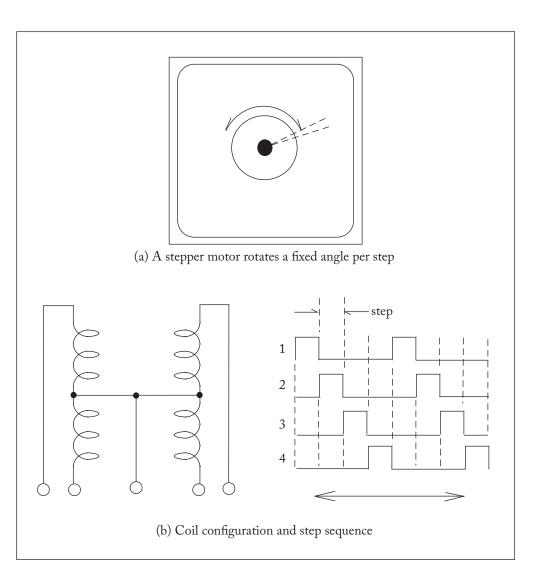

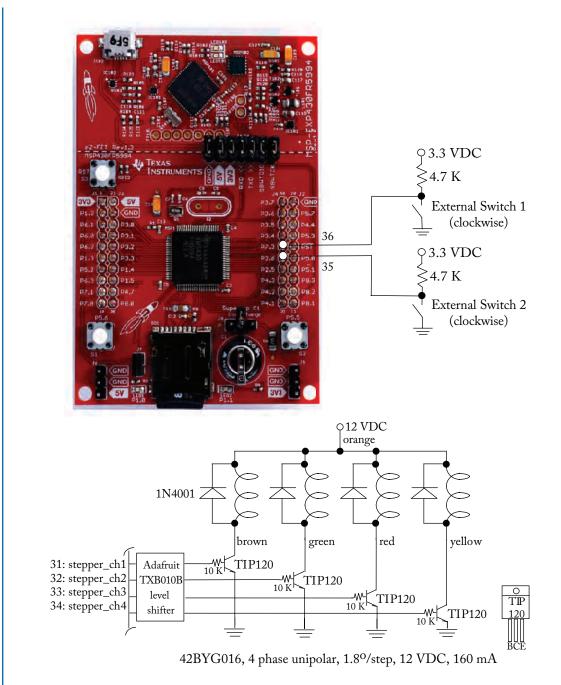

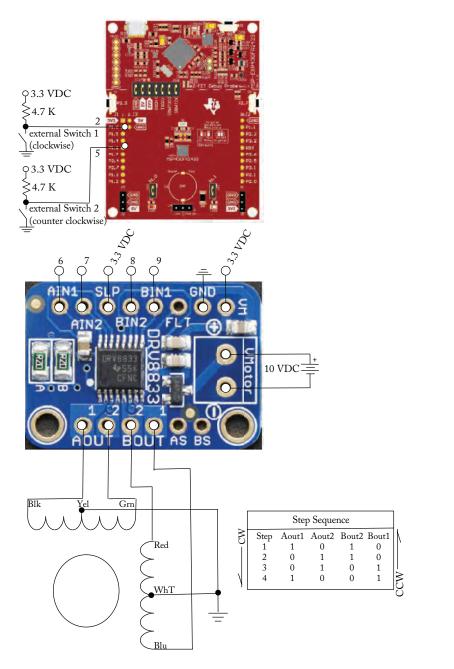

|   |       | 4.4.3 Stepper Motor Control                                            | . 185 |

|   |       | 4.4.4 Optical Isolation                                                | . 197 |

|   | 4.5   | Interfacing to Miscellaneous DC Devices                                |       |

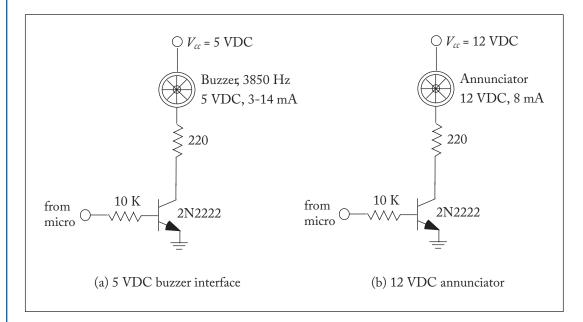

|   |       | 4.5.1 Sonalerts, Beepers, and Buzzers                                  | . 198 |

|   |       | 4.5.2 Vibrating Motor                                                  |       |

|   |       | 4.5.3 DC Fan                                                           |       |

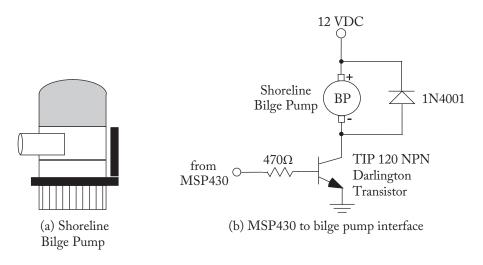

|   |       | 4.5.4 Bilge Pump                                                       |       |

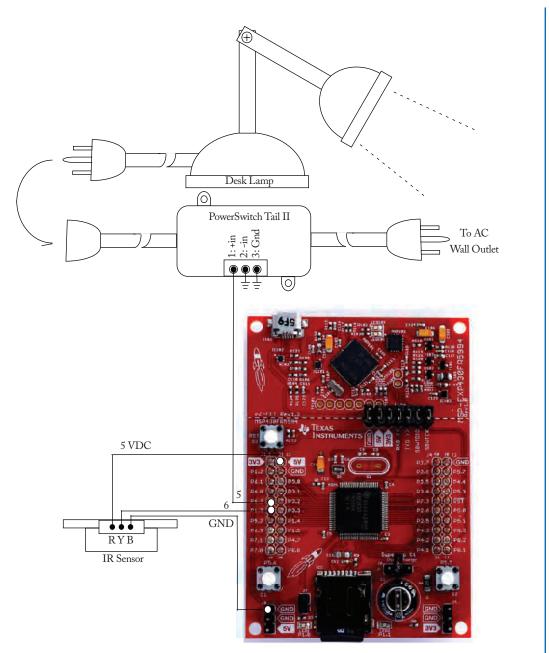

|   | 4.6   | AC Devices                                                             | . 199 |

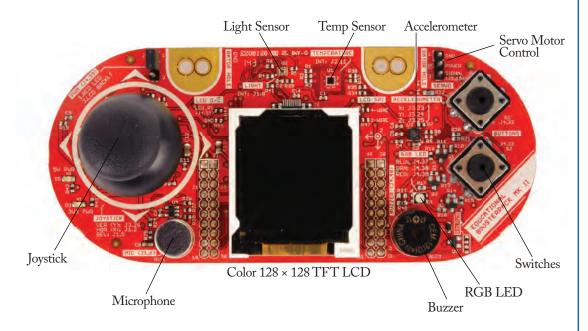

|   | 4.7   | MSP430FR5994: Educational Booster Pack MkII                            | . 203 |

|   | 4.8   | Grove Starter Kit for LaunchPad                                        | . 205 |

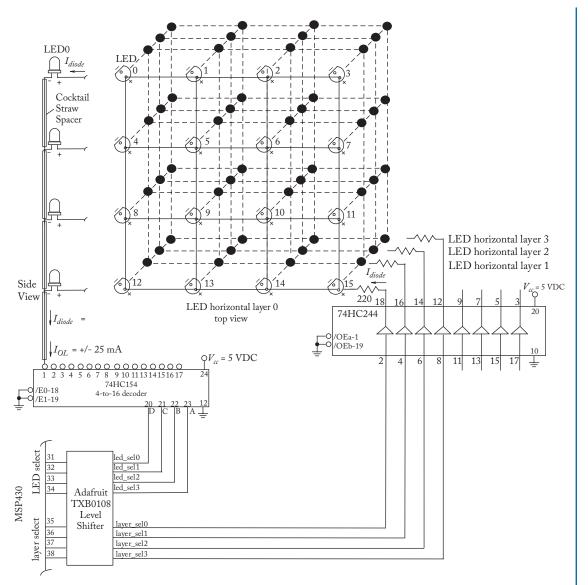

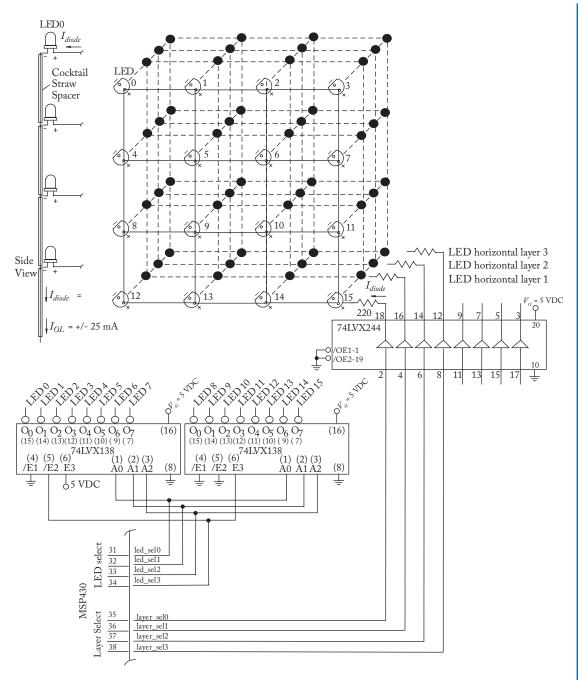

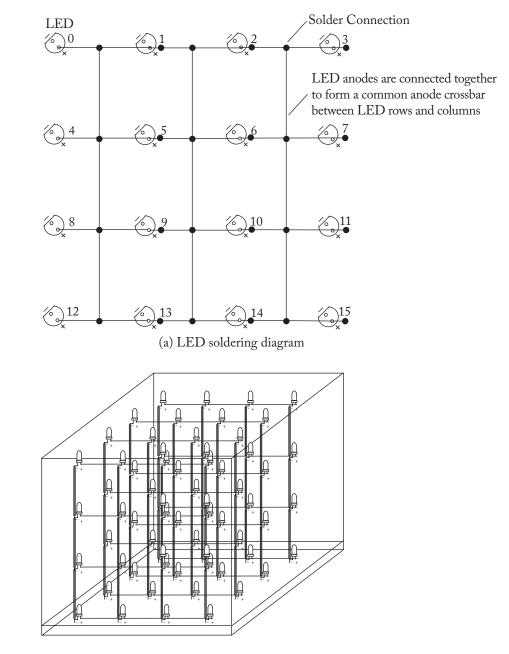

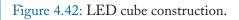

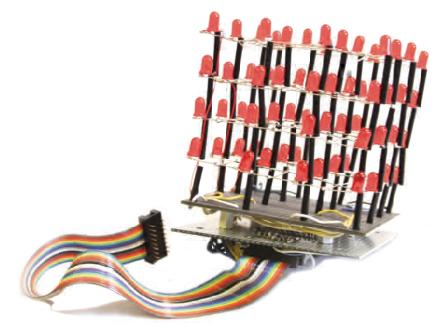

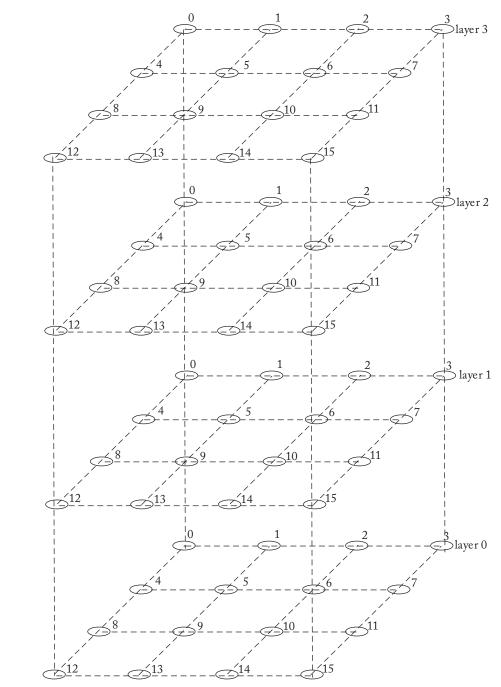

|   | 4.9   | Application: Special Effects LED Cube                                  | . 205 |

|   |       | 4.9.1 Construction Hints                                               | . 208 |

|   |       | 4.9.2 LED Cube MSP430 Energia Code                                     | . 211 |

|   | 4.10  | Laboratory Exercise: Introduction to the Educational Booster Pack MkII | 224   |

|   | 4 1 1 | and the Grove Starter Kit                                              |       |

|   | 4.11  | Laboratory: Collection and Display of Weather Information              |       |

|   | 4.12  | Summary                                                                |       |

|   | 4.13  | References and Further Reading                                         |       |

|   | 4.14  | Chapter Problems                                                       | . 229 |

| 5 | Powe  | er Management and Clock Systems                                        | . 231 |

|   | 5.1   | Overview                                                               |       |

|   | 5.2   | Background Theory                                                      | . 232 |

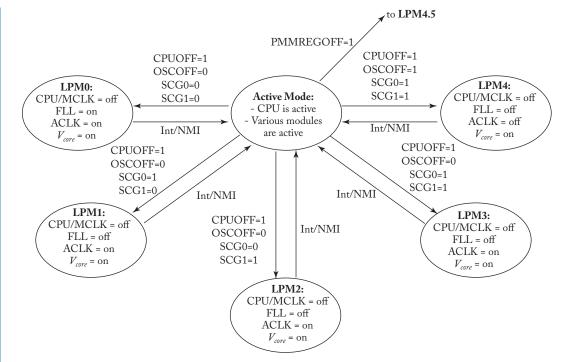

|   | 5.3   | Operating Modes                                                        |       |

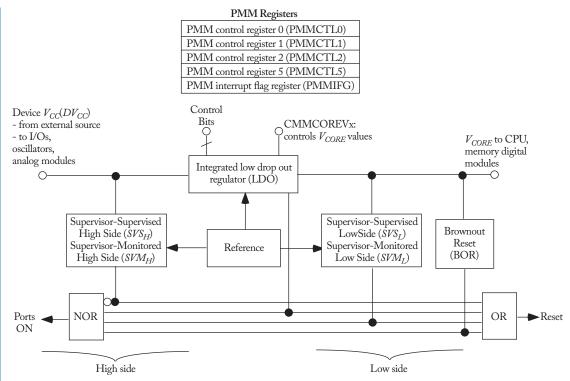

|   | 5.4   | The Power Management Module (PMM) and Supply Voltage Supervisor        |       |

|   |       | (SVS)                                                                  | . 239 |

|   |       | 5.4.1 Supply Voltage Supervisor                                        | . 239 |

|      | xv                                                                    | ii |

|------|-----------------------------------------------------------------------|----|

|      | 5.4.2 PMM Registers                                                   |    |

| 5.5  | Clock System                                                          |    |

| 5.6  | Battery Operation                                                     |    |

| 5.7  | Voltage Regulation                                                    |    |

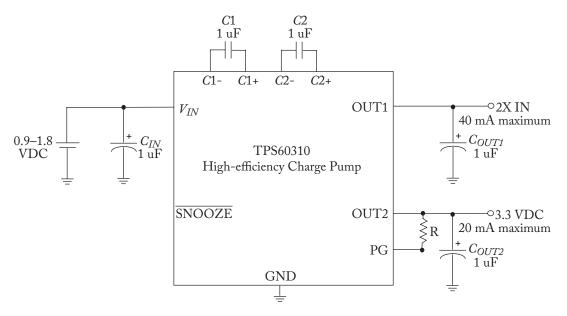

| 5.8  | High-Efficiency Charge Pump Circuits                                  |    |

| 5.9  | Laboratory Exercise: MSP430 Power Systems and Low-Power Mode          |    |

|      | Operation                                                             |    |

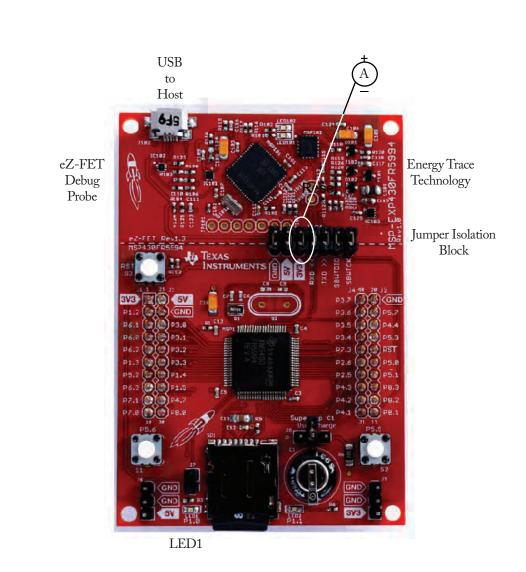

|      | 5.9.1 Current Measurements in Different Operating Modes 251           |    |

|      | 5.9.2 Operating an MSP430 from a Single Regulated Battery Source 252  |    |

|      | 5.9.3 Operating an MSP430 from a Single 1.5 VDC Battery 252           |    |

| 5.10 | Summary                                                               |    |

| 5.11 | References and Further Reading                                        |    |

| 5.12 | Chapter Problems                                                      |    |

| MSP  | 430 Memory System                                                     |    |

| 6.1  | Overview                                                              |    |

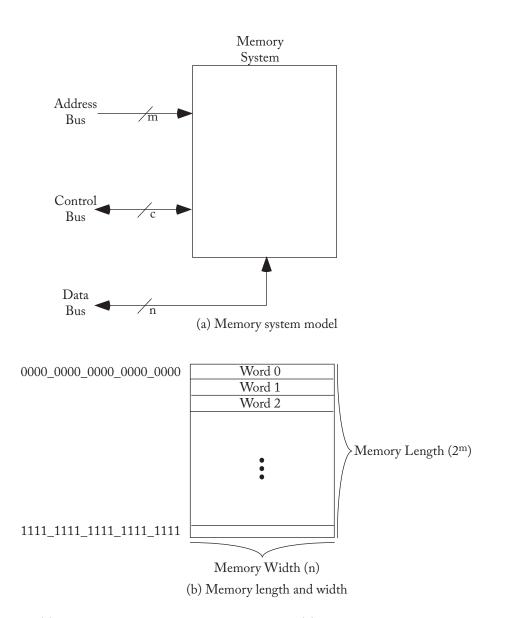

| 6.2  | Basic Memory Concepts                                                 |    |

|      | 6.2.1 Memory Buses                                                    |    |

|      | 6.2.2 Memory Operations 258                                           |    |

|      | 6.2.3 Binary and Hexadecimal Numbering Systems 259                    |    |

|      | 6.2.4 Memory Architectures                                            |    |

|      | 6.2.5 Memory Types                                                    |    |

|      | 6.2.6 Memory Map                                                      |    |

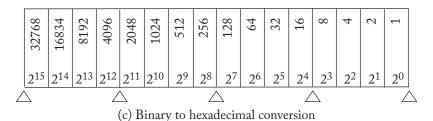

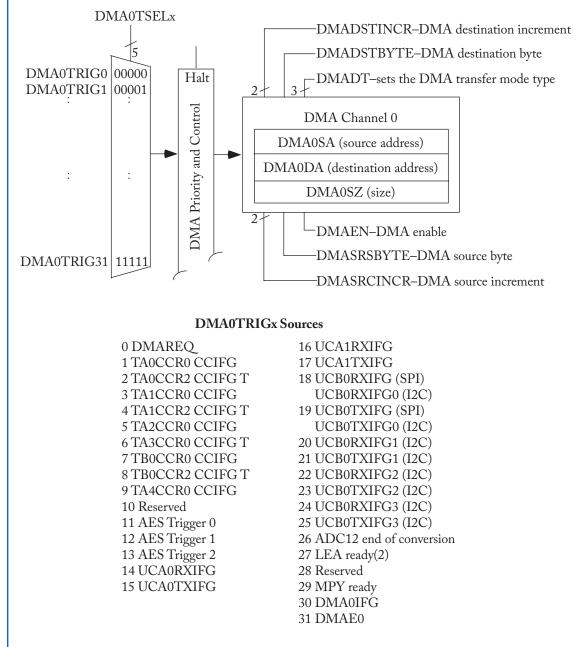

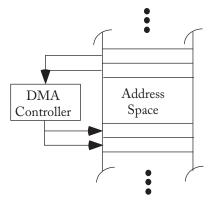

|      | 6.2.7 Direct Memory Access (DMA)                                      |    |

| 6.3  | Aside: Memory Operations in C Using Pointers                          |    |

| 6.4  | Direct Memory Access (DMA) controller                                 |    |

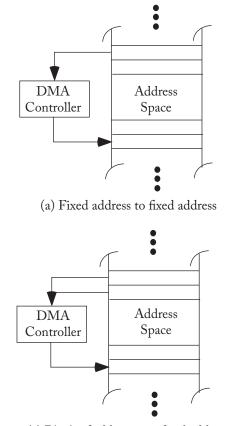

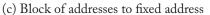

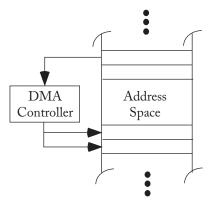

|      | 6.4.1 DMA System                                                      |    |

|      | 6.4.2 DMA Example: Block Transfer                                     |    |

| 6.5  | MSP430FR5994: Memory Protection Unit and IP Encapsulation Segment 276 |    |

| 6.6  | External Memory: Bulk Storage with an MMC/SD Card 277                 |    |

| 6.7  | Laboratory Exercise: SD Card Operations with the MSP-EXP430FR5994 277 |    |

| 6.8  | Laboratory Exercise: MSP-EXP430FR5994 LaunchPad DMA Transfer 278      |    |

| 6.9  | Summary                                                               |    |

| 6.10 | References and Further Reading                                        |    |

| 6.11 | Chapter Problems                                                      |    |

6

|    |   | • |   |

|----|---|---|---|

| XV | 1 | 1 | 1 |

|    | - | - |   |

| Time | er Systems                                                       |     |

|------|------------------------------------------------------------------|-----|

| 7.1  | Introduction                                                     | 281 |

| 7.2  | Motivation: Real-Time Location Systems (RTLS)                    |     |

| 7.3  | Time-Related Signal Parameters                                   |     |

|      | 7.3.1 Frequency                                                  |     |

|      | 7.3.2 Period                                                     | 282 |

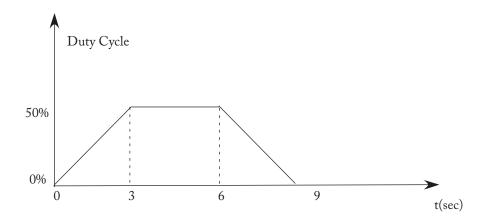

|      | 7.3.3 Duty Cycle                                                 | 283 |

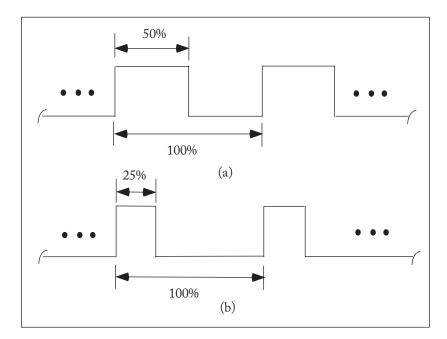

|      | 7.3.4 Pulse Width Modulation                                     | 284 |

| 7.4  | Overview of MSP430 Timer Features                                | 285 |

| 7.5  | Energia-Related Time Functions                                   | 286 |

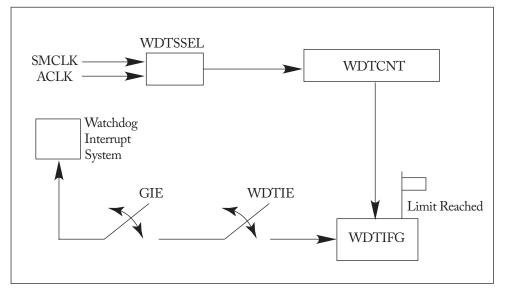

| 7.6  | Watchdog Timer                                                   | 288 |

|      | 7.6.1 Protecting from Software Failure                           | 288 |

|      | 7.6.2 Interval Timer                                             | 290 |

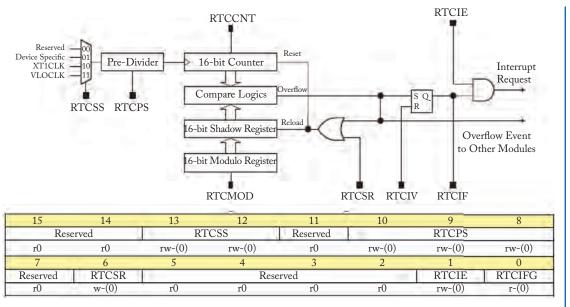

| 7.7  | Real-Time Clock                                                  | 292 |

| 7.8  | Real-Time Clock-MSP430FR2433                                     | 292 |

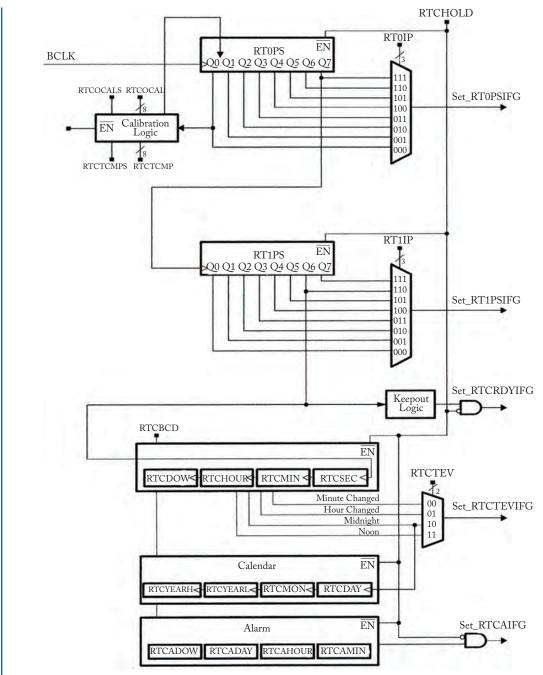

|      | 7.8.1 Real-Time Clock: RTC_B, RTC_C-MSP430FR5994                 | 295 |

|      | 7.8.2 RTC Registers                                              | 297 |

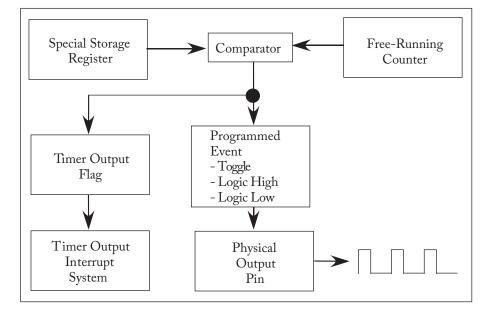

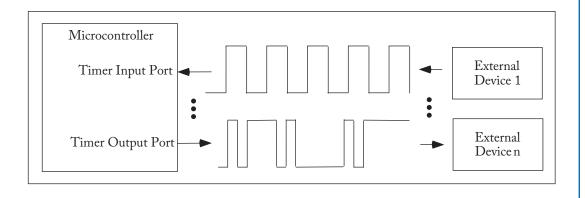

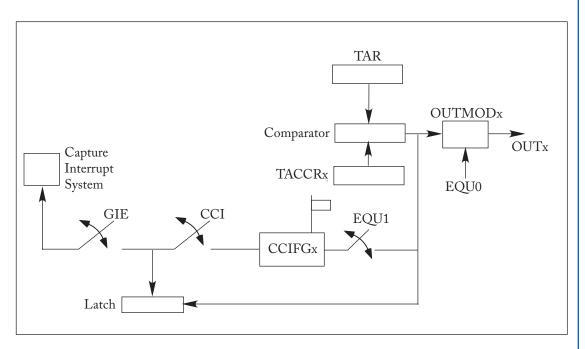

| 7.9  | Input Capture and Output Compare Features                        | 302 |

|      | 7.9.1 Timing System Overview and Background Theory               | 302 |

|      | 7.9.2 Applications                                               | 305 |

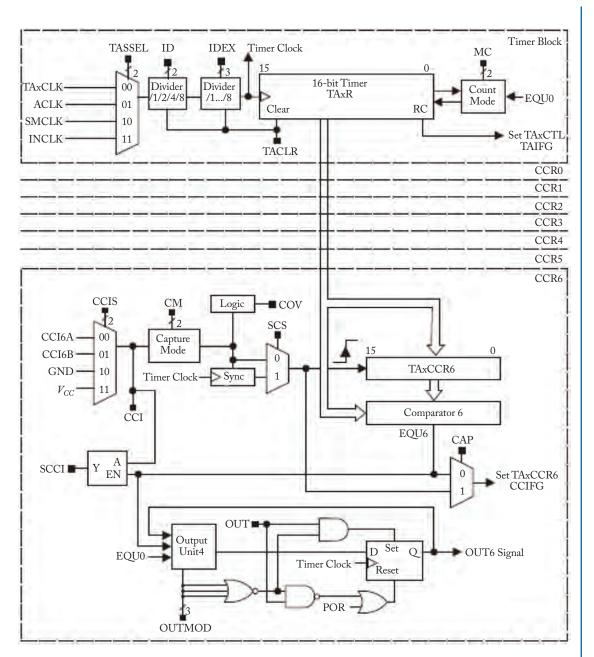

| 7.10 | MSP430 Timers: Timer_A and Timer_B                               | 307 |

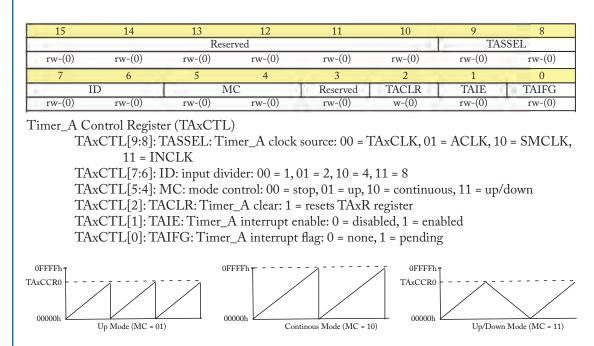

|      | 7.10.1 MSP430 Free Running Counter                               | 308 |

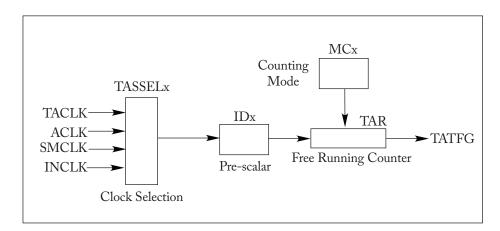

|      | 7.10.2 Input Capture                                             |     |

|      | 7.10.3 Output Compare                                            |     |

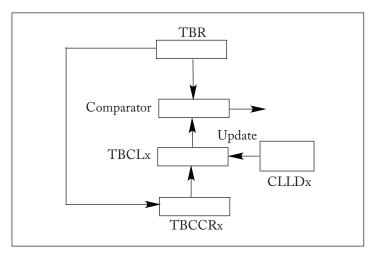

|      | 7.10.4 Timer_B System                                            | 321 |

| 7.11 | Laboratory Exercise: Generation of Varying Pulse Width Modulated |     |

|      | Signals to Control DC Motors                                     |     |

| 7.12 | Summary                                                          |     |

| 7.13 | References and Further Reading                                   | 327 |

| 7.14 | Chapter Problems                                                 | 328 |

| Rese | ts and Interrupts                                                | 331 |

| 8.1  | Motivation                                                       | 331 |

| 8.2  | Background                                                       | 332 |

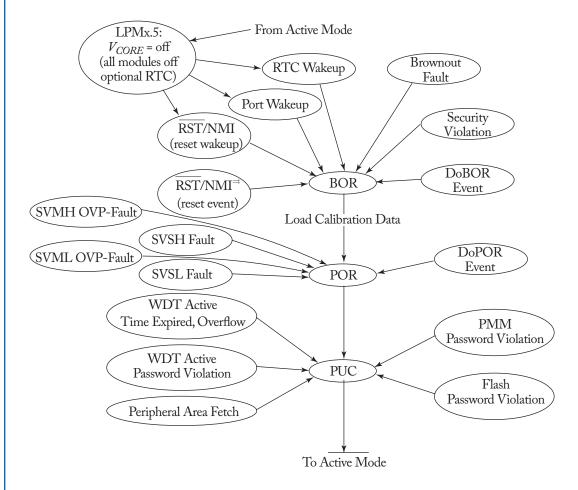

| 8.3  | MSP430 Resets/Interrupts Overview                                |     |

| 8.4  | MSP430 Resets                                                    |     |

|    | 8.5  | Interrupts                                            |

|----|------|-------------------------------------------------------|

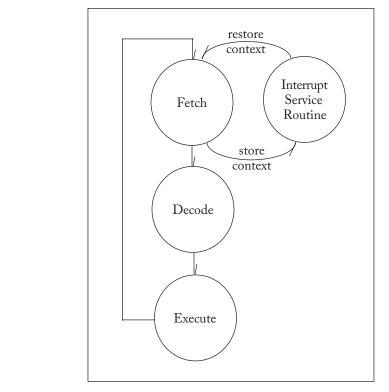

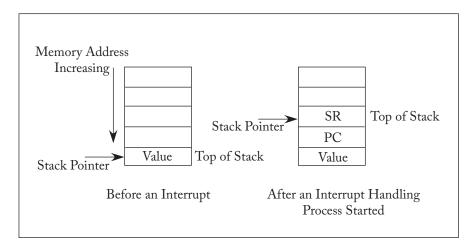

|    |      | 8.5.1 Interrupt Handling Process                      |

|    |      | 8.5.2 Interrupt Priority                              |

|    |      | 8.5.3 Interrupt Service Routine (ISR)                 |

|    | 8.6  | Laboratory Exercise                                   |

|    | 8.7  | References and Further Reading                        |

|    | 8.8  | Chapter Problems                                      |

| 9  | Anal | og Peripherals                                        |

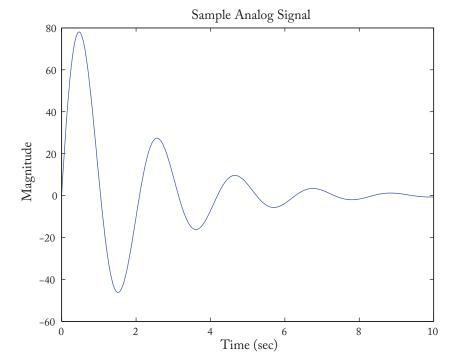

|    | 9.1  | Analog-to-Digital Conversion Process                  |

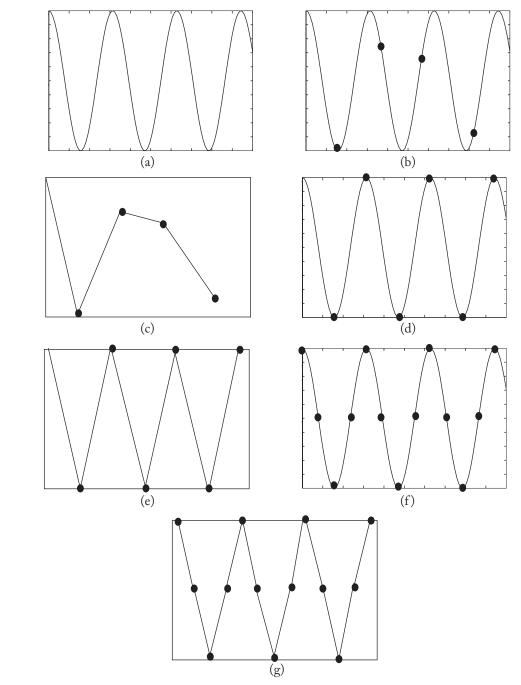

|    |      | 9.1.1 Sampling                                        |

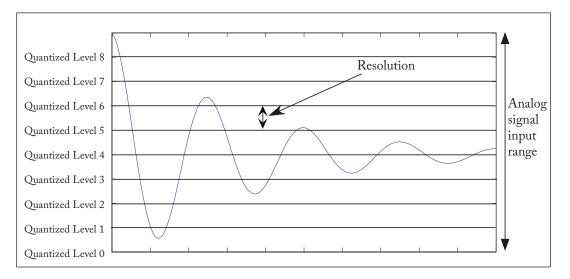

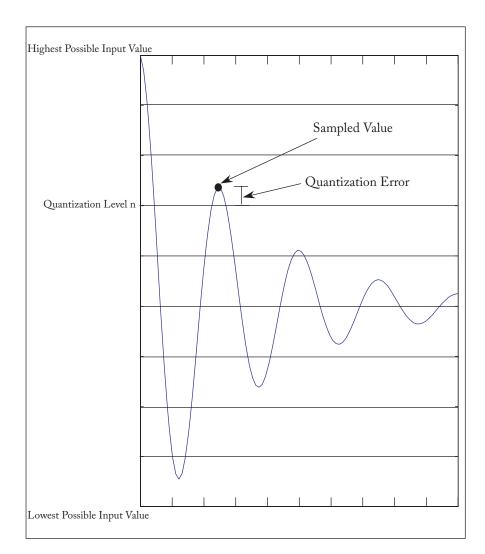

|    |      | 9.1.2 Quantization                                    |

|    |      | 9.1.3 Encoding                                        |

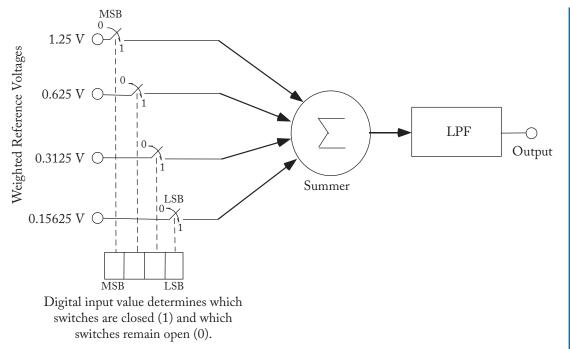

|    | 9.2  | Digital-to-Analog Converter Process                   |

|    | 9.3  | MSP430 ADC Systems                                    |

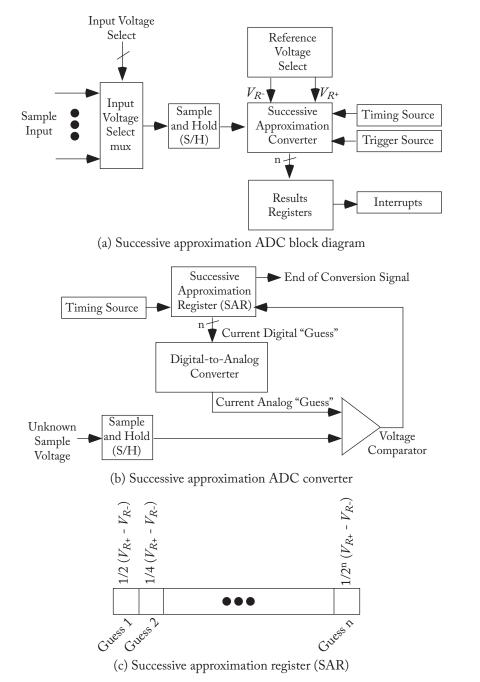

|    |      | 9.3.1 MSP 430 ADC Block Diagram                       |

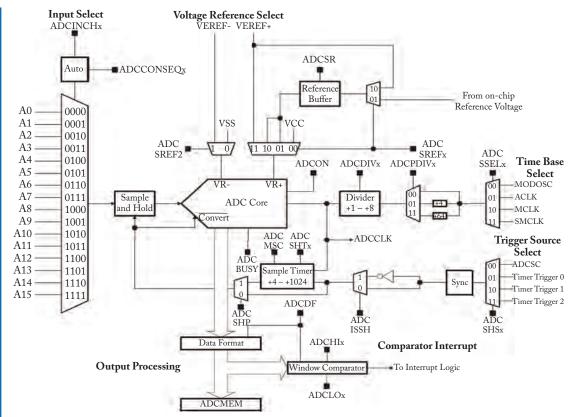

|    |      | 9.3.2 MSP430FR2433 10-bit Analog-to-Digital Converter |

|    |      | 9.3.3 MSP430FR2433 Register Summary                   |

|    |      | 9.3.4 Programming the MSP430FR2433 ADC in C           |

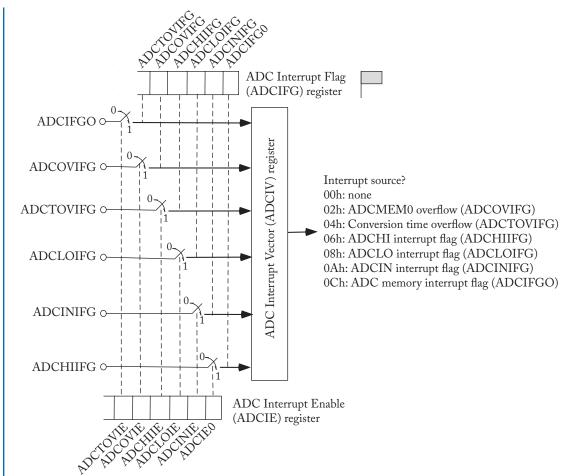

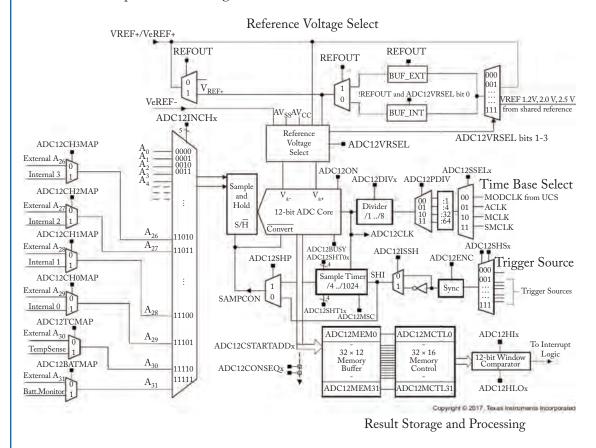

|    | 9.4  | MSP430FR5994 Analog-to-Digital Converter              |

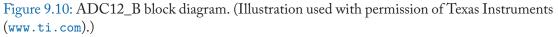

|    |      | 9.4.1 ADC12_B Features                                |

|    |      | 9.4.2 MSP430FR5994 ADC12_B Operation                  |

|    |      | 9.4.3 MSP430FR5994 Register Summary 379               |

|    |      | 9.4.4 Analysis of Results                             |

|    |      | 9.4.5 Programming the MSP430FR5994 ADC12_B System     |

|    | 9.5  | MSP430FR5994 Comparator                               |

|    | 9.6  | Advanced Analog Peripherals                           |

|    |      | 9.6.1 Smart Analog Combo (SAC)                        |

|    |      | 9.6.2 Enhanced Comparator (eCOMP) 390                 |

|    |      | 9.6.3 Transimpedance Amplifier (TIA)                  |

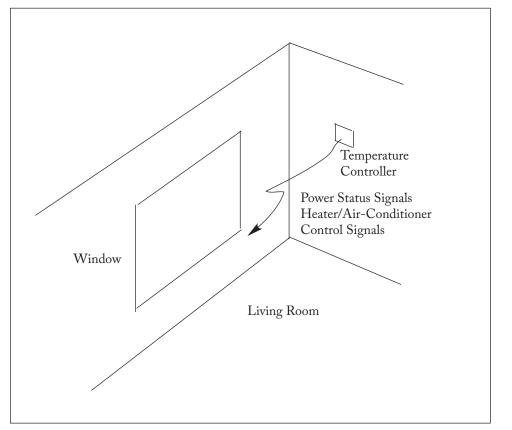

|    | 9.7  | Laboratory Exercise: Smart Home Sensor390             |

|    | 9.8  | References and Further Reading                        |

|    | 9.9  | Chapter Problems                                      |

| 10 | Com  | munication Systems                                    |

|    | 10.1 | Background                                            |

|    | 10.2 | Serial Communication Concepts                         |

xix

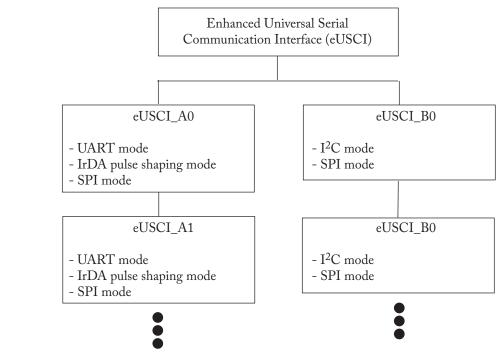

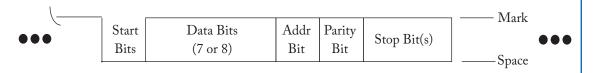

|    | 10.3  | MSP430 UART                                                                                       |

|----|-------|---------------------------------------------------------------------------------------------------|

|    |       | 10.3.1 UART Features                                                                              |

|    |       | 10.3.2 UART Overview                                                                              |

|    |       | 10.3.3 Character Format 402                                                                       |

|    |       | 10.3.4 Baud Rate Selection 402                                                                    |

|    |       | 10.3.5 UART Associated Interrupts 403                                                             |

|    |       | 10.3.6 UART Registers 404                                                                         |

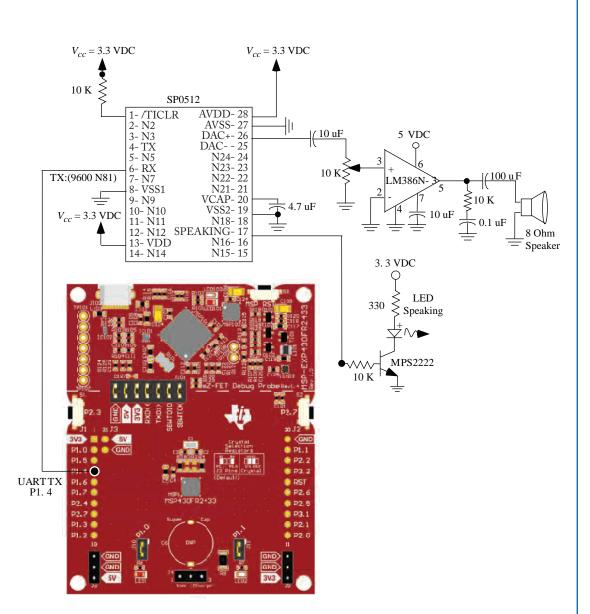

|    | 10.4  | Code Examples                                                                                     |

|    |       | 10.4.1 Energia                                                                                    |

|    |       | 10.4.2 UART C Example 408                                                                         |

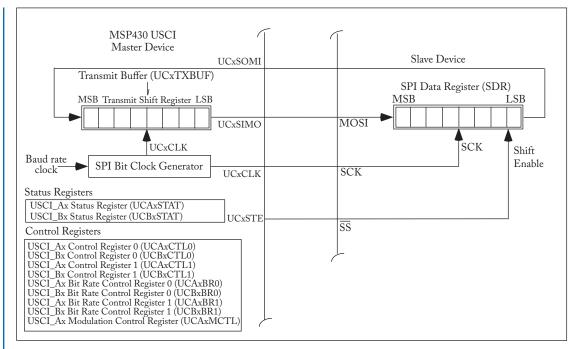

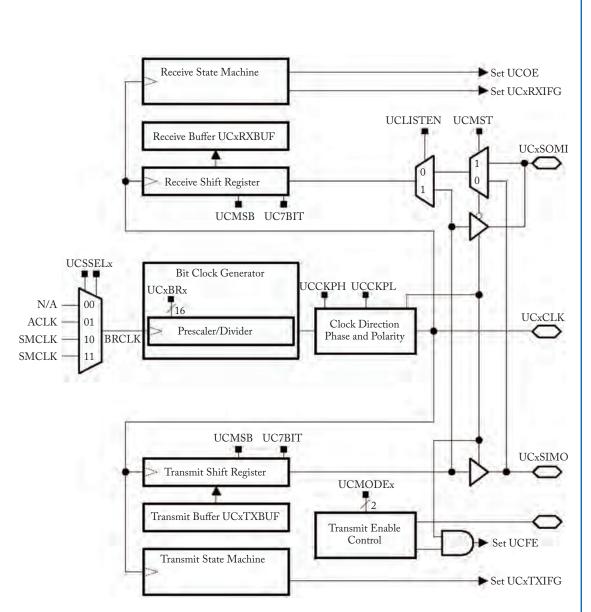

|    | 10.5  | Serial Peripheral Interface-SPI 411                                                               |

|    |       | 10.5.1 SPI Operation 411                                                                          |

|    |       | 10.5.2 MSP430 SPI Features 411                                                                    |

|    |       | 10.5.3 MSP430 SPI Hardware Configuration 412                                                      |

|    |       | 10.5.4 SPI Registers 414                                                                          |

|    |       | 10.5.5 SPI Code Examples 416                                                                      |

|    | 10.6  | Inter-Integrated Communication – $I^2C$ Module                                                    |

|    |       | 10.6.1 I <sup>2</sup> C Initialization                                                            |

|    |       | 10.6.2 $I^2C$ Protocol                                                                            |

|    |       | 10.6.3 MSP430 as a Slave Device                                                                   |

|    |       | 10.6.4 MSP430 as a Master Device                                                                  |

|    |       | 10.6.5 $I^2C$ Registers                                                                           |

|    |       | 10.6.6 Programming the $I^2C$                                                                     |

|    | 10.7  | Laboratory Exercise: UART and SPI Communications                                                  |

|    | 10.8  | Summary 458                                                                                       |

|    | 10.9  | References and Further Reading 458                                                                |

|    | 10.10 | Chapter Problems                                                                                  |

| 11 | MSP   | 2430 System Integrity                                                                             |

|    | 11.1  | Overview                                                                                          |

|    | 11.1  |                                                                                                   |

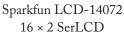

|    | 11.4  | Electromagnetic Interference46211.2.1 EMI reduction Strategies462                                 |

|    | 11.3  |                                                                                                   |

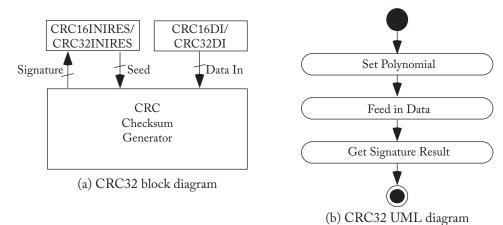

|    | 11.3  | Cyclic Redundancy Check46411.3.1 MSP430FR5994 CRC32 Module465                                     |

|    |       | 11.3.1       MSI 4507 K5994 CRC32 Module       465         11.3.2       CRC16 Registers       466 |

|    |       | 11.3.3 CRC32 Registers                                                                            |

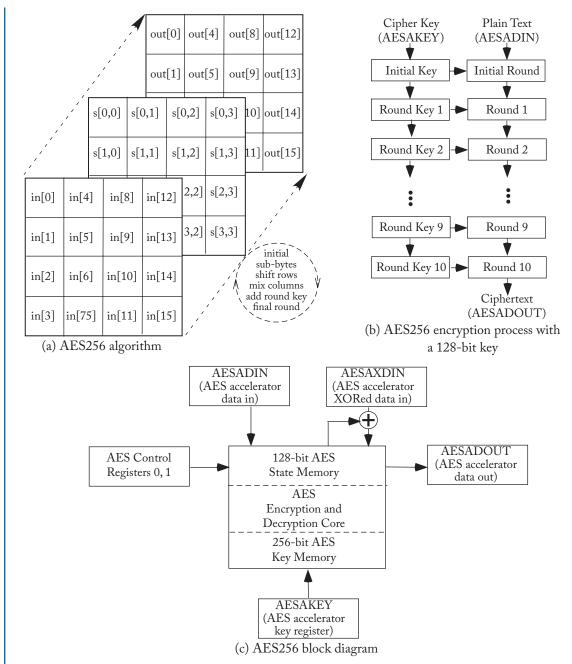

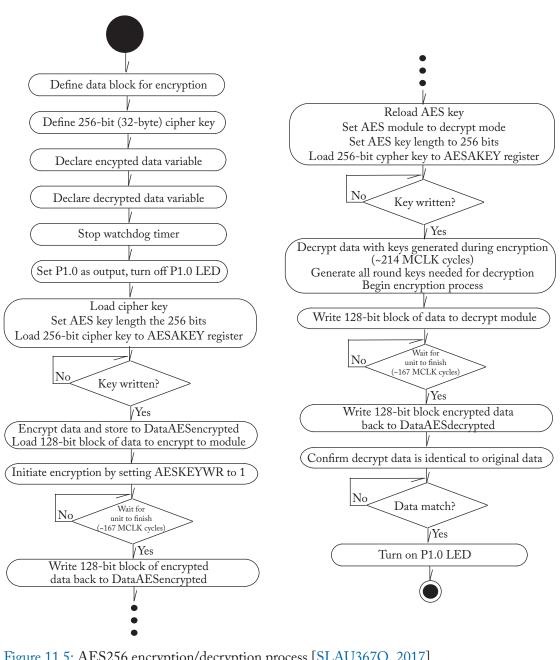

|    | 11.4  | AES256 Accelerator Module                                                                         |

| 1  | 11.4  | 1110230 / icecieiator module                                                                      |

|    |       | 11.4.1 Registers                           |

|----|-------|--------------------------------------------|

|    |       | 11.4.2 API Support                         |

|    | 11.5  | Laboratory Exercise: AES256                |

|    | 11.6  | Summary                                    |

|    | 11.7  | References and Further Reading             |

|    | 11.8  | Chapter Problems                           |

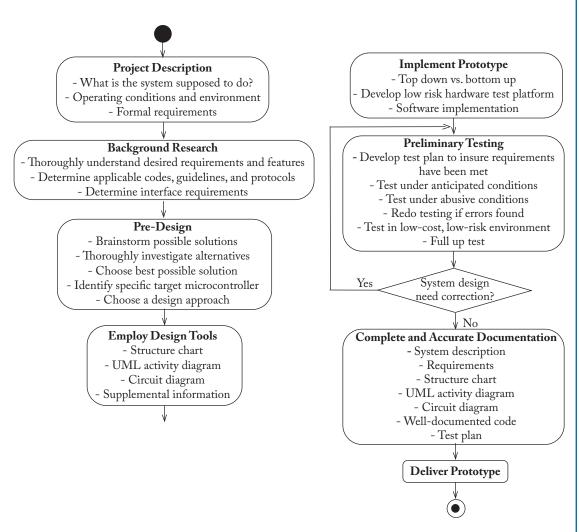

| 12 | Syste | em-Level Design                            |

|    | 12.1  | Overview                                   |

|    | 12.2  | What is an Embedded System?                |

|    | 12.3  | Embedded System Design Process             |

|    |       | 12.3.1 Project Description                 |

|    |       | 12.3.2 Background Research                 |

|    |       | 12.3.3 Pre-Design                          |

|    |       | 12.3.4 Design                              |

|    |       | 12.3.5 Implement Prototype 492             |

|    |       | 12.3.6 Preliminary Testing                 |

|    |       | 12.3.7 Complete and Accurate Documentation |

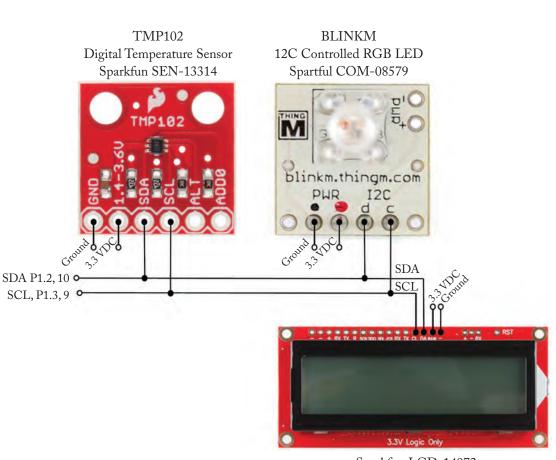

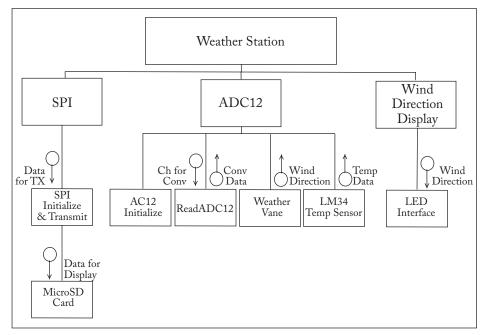

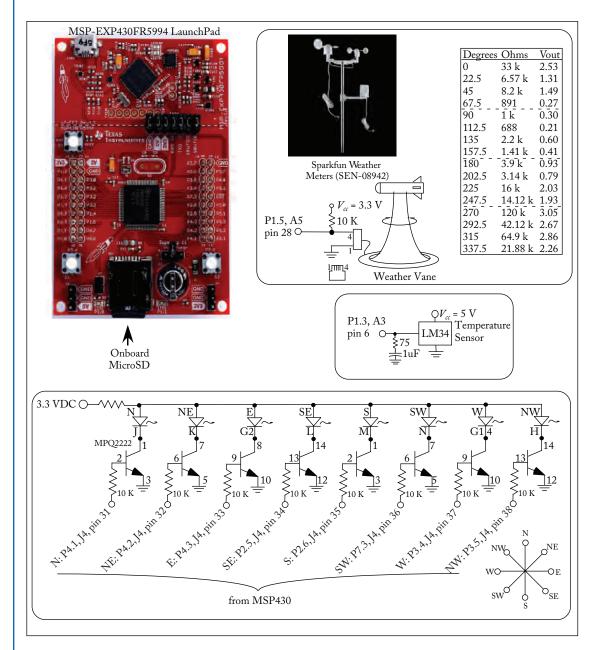

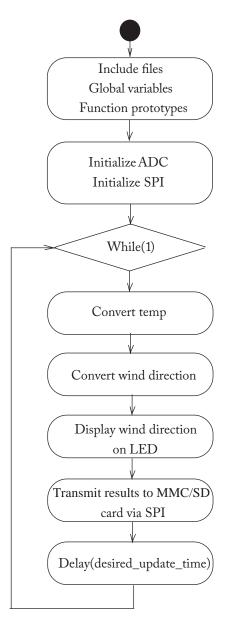

|    | 12.4  | MSP430FR5994: Weather Station              |

|    |       | 12.4.1 Requirements                        |

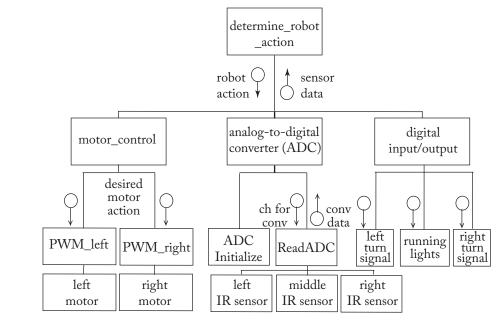

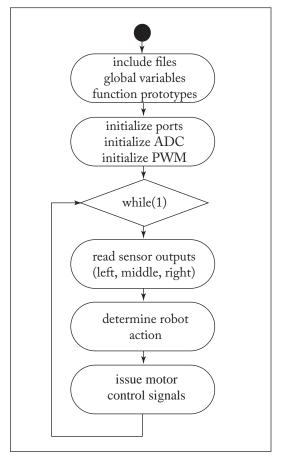

|    |       | 12.4.2 Structure Chart                     |

|    |       | 12.4.3 Circuit Diagram                     |

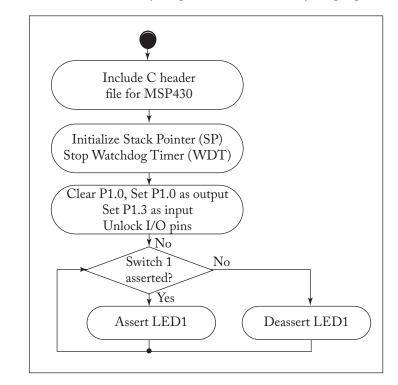

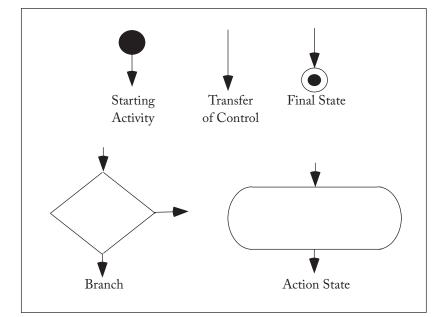

|    |       | 12.4.4 UML Activity Diagrams               |

|    |       | 12.4.5 Microcontroller Code                |

|    |       | 12.4.6 Project Extensions                  |

|    | 12.5  | Submersible Robot                          |

|    |       | 12.5.1 Approach                            |

|    |       | 12.5.2 Requirements                        |

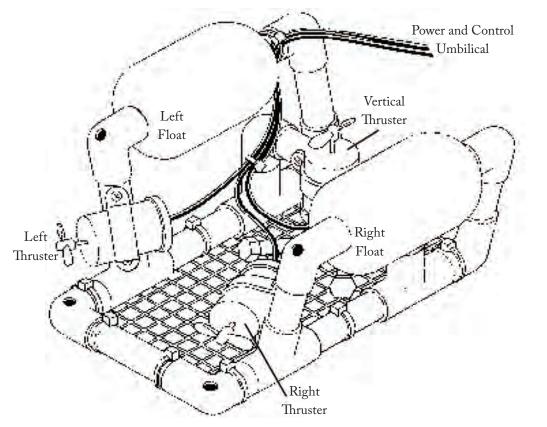

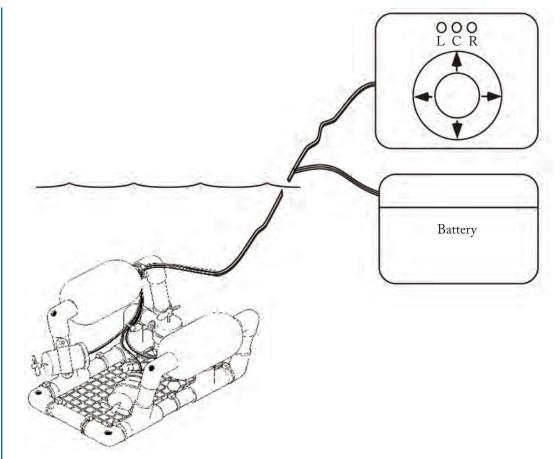

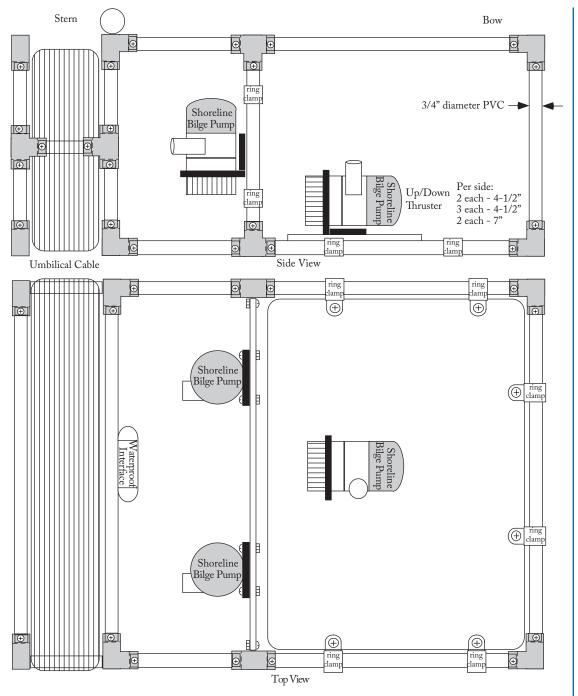

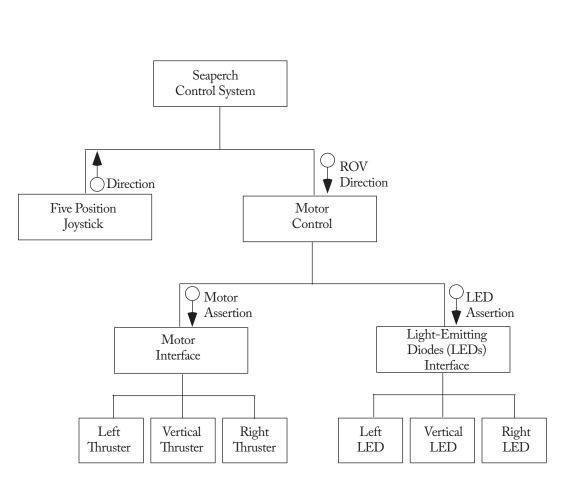

|    |       | 12.5.3 ROV Structure                       |

|    |       | 12.5.4 Structure Chart                     |

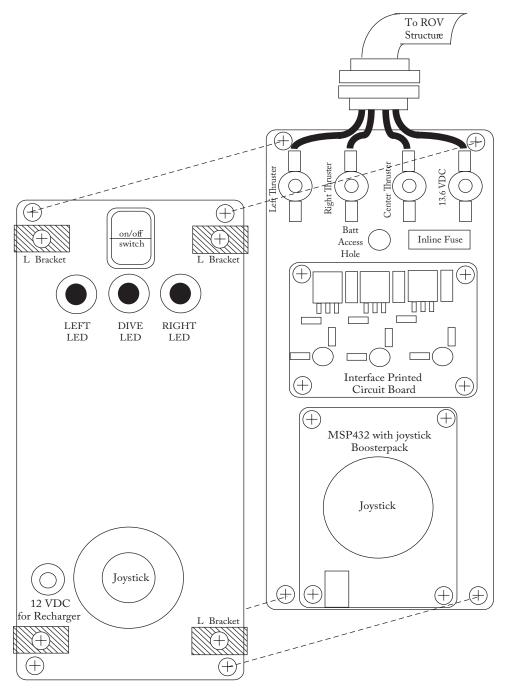

|    |       | 12.5.5 Circuit Diagram                     |

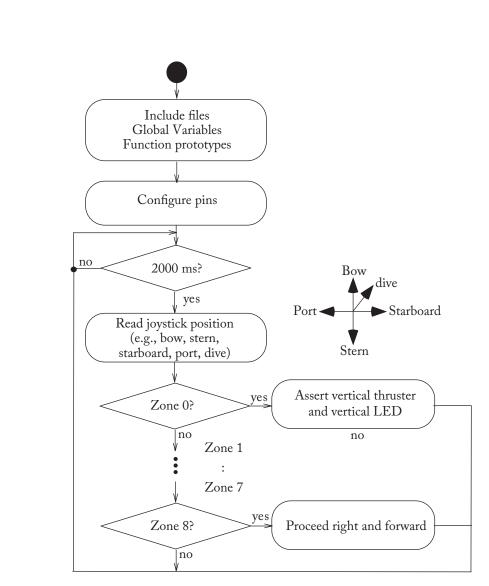

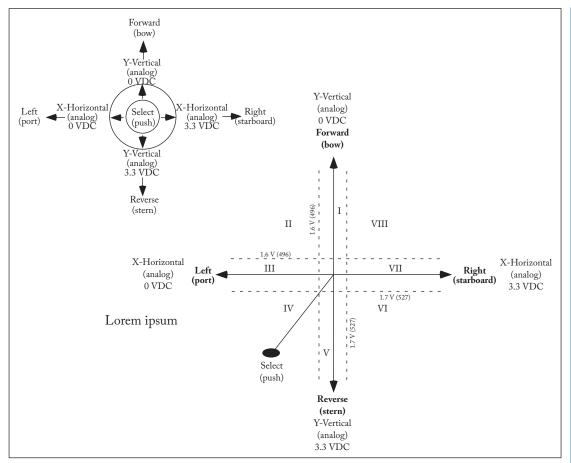

|    |       | 12.5.6 UML Activity Diagram                |

|    |       | 12.5.7 MSP430 Code                         |

|    |       | 12.5.8 Control Housing Layout              |

|    |       | 12.5.9 Final Assembly Testing              |

|    |       | 12.5.10 Final Assembly                     |

|    |       | 12.5.11 Project Extensions                 |

xxii

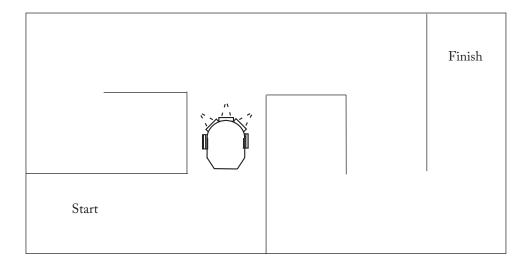

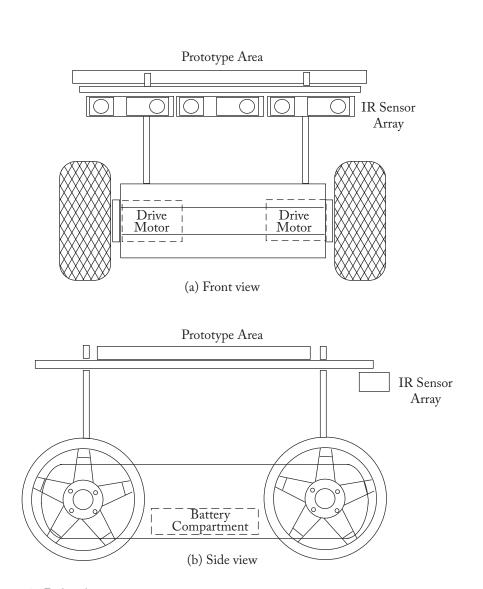

| 12.6 | Mountain Maze Navigating Robot 5 | 28 |

|------|----------------------------------|----|

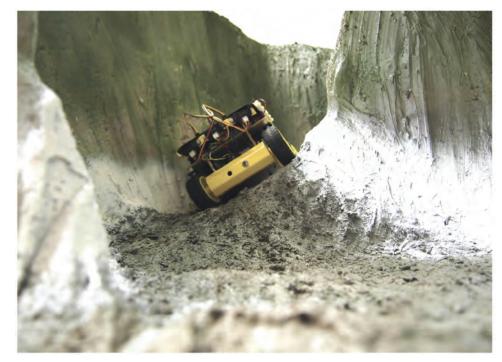

|      | 12.6.1 Description               | 28 |

|      | 12.6.2 Requirements 5            | 28 |

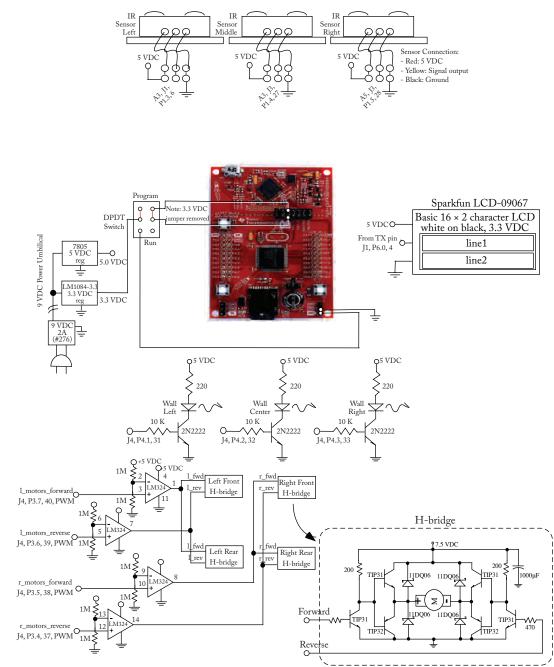

|      | 12.6.3 Circuit Diagram 5         | 28 |

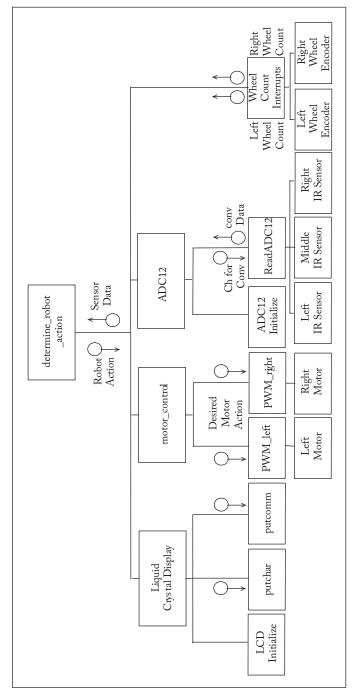

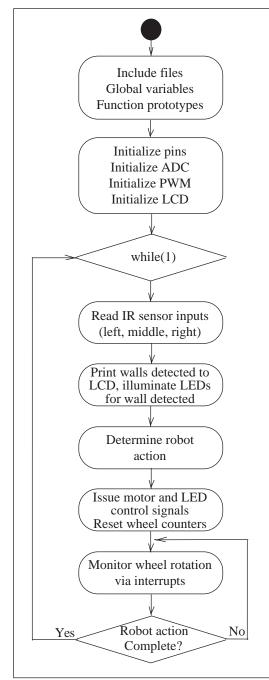

|      | 12.6.4 Structure Chart 5         | 28 |

|      | 12.6.5 UML Activity Diagrams 5   | 28 |

|      | 12.6.6 Robot Code                | 33 |

|      | 12.6.7 Mountain Maze 5           | 40 |

|      | 12.6.8 Project Extensions 5      | 40 |

| 12.7 | Summary 5                        | 42 |

| 12.8 | References and Further Reading 5 | 43 |

| 12.9 | Chapter Exercises                | 44 |

| Auth | ors' Biographies                 | 47 |

| Inde |                                  | 49 |

## Preface

Texas Instruments is well known for its analog and digital devices, in particular, Digital Signal Processing (DSP) chips. Unknown to many, the company quietly developed its microcontroller division in the early 1990s and started producing a family of controllers aimed mainly for embedded meter applications, which require an extended operating time without intervention for power companies. It was not until the mid 2000s that the company began serious effort to present the MSP430 microcontroller family, its flagship microcontroller, to the academic community and future engineers. Their efforts have been quietly attracting many educators and students due to the MSP430's cost and the suitability of the controller for capstone design projects requiring microcontrollers. In addition, Texas Instruments offers many compatible analog and digital devices that can expand the range of the possible embedded applications of the microcontroller. Texas Instruments has continually added new innovation to the MSP430 microcontroller line. The second edition introduces the MSP–EXP430FR5994 and the MSP–EXP430FR2433 LaunchPads. Both LaunchPads are equipped with a variety of peripherals and Ferroelectric Random Access Memory (FRAM). FRAM is a nonvolatile, low-power memory with functionality similar to flash memory.

This book is about the MSP430 microcontroller family. We have three goals in writing this book. The first is to introduce readers to microcontroller programming. The MSP430 microcontrollers can be programmed either using assembly language or a high–level programming language such as C. The second goal of the book is to teach students how computers work. After all, a microcontroller is a computer within a single integrated circuit (chip). Finally, we present the microcontroller's input/output interface capabilities, one of the main reasons for developing embedded systems with microcontrollers.

### Background

This book provides a thorough introduction to the Texas Instruments MSP430 microcontroller. The MSP430 is a 16-bit reduced instruction set (RISC) processor that features ultra-low power consumption and integrated digital and analog hardware. Variants of the MSP430 microcontroller have been in production since 1993 with a host of MSP430-related products including evaluation boards, compilers, software examples, and documentation.

This book is intentionally tutorial in nature with many worked examples, illustrations, and laboratory exercises. An emphasis is placed on real-world applications such as smart home concepts, mobile robots, an unmanned underwater vehicle, and a DC motor controller to name a few.

xxiii

#### xxiv PREFACE

### **Intended Readers**

The book is intended for an upper level undergraduate course in microcontrollers or mechatronics but may also be used as a reference for capstone design projects. Also, practicing engineers who are already familiar with another line of microcontrollers, but require a quick tutorial on the MSP430 microcontroller, will find this book beneficial.

### Approach and Organization

This book provides a thorough introduction to the MSP430 line of microcontrollers, programming techniques, and interface concepts. Each chapter contains a list of objectives, background tutorial information, and detailed information on the operation of the MSP430 system under study. Furthermore, each chapter provides laboratory exercises to apply what has been presented in the chapter and how the concepts are employed in real applications. Each chapter concludes with a series of homework exercises divided into Fundamental, Advanced, and Challenging categories. The reader will get the most out of the book by also having the following references readily available:

- MSP430FR2433 Mixed-Signal Microcontroller, SLASE59B;

- MSP430FR4xx and MSP430FR2xx Family User's Guide, SLAU445G;

- MSP430FR599x, MSP430FR596x Mixed-Signal Microcontrollers, SLASE54B; and

- MSP430FR58xx, MSP430FR59xx, and MSP430FR6xx Family User's Guide, SLAU367O.

This documentation is available for download from the Texas Instruments website [www.ti.com].

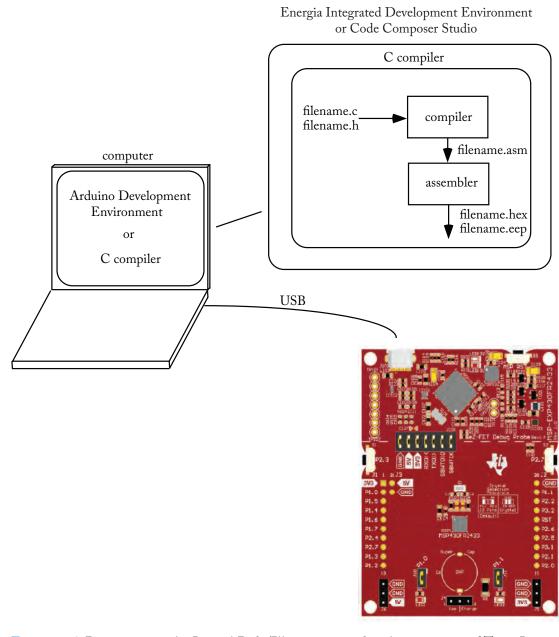

Chapter 1 provides a brief review of microcontroller terminology and a short history followed by an overview of the MSP430 microcontroller. The overview surveys systems onboard the microcontroller and also various MSP430 families. The chapter concludes with an introduction to the hardware and software development tools that will be used for the remainder of the book. Our examples employ the MSP–EXP430FR5994 and the MSP430FR2433 LaunchPads, the Energia rapid prototyping platform, and the Texas Instruments' Code Composer Studio Integrated Development Environment (IDE). The information provided can be readily adapted to other MSP430 based experimenter boards.

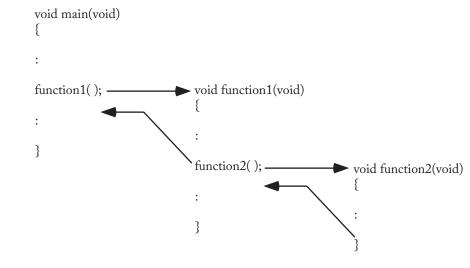

Chapter 2 provides a brief introduction to programming in C. The chapter contains multiple examples for a new programmer. It also serves as a good review for seasoned programmers. Also, software programming tools including Energia, Code Composer Studio IDE, and debugging tools are explored. This chapter was adapted from material originally written for the Texas Instruments MSP432, a 32-bit processor that has close ties to the 16-bit MSP430.<sup>1</sup> Embed-

<sup>1</sup>This chapter was adapted with permission from *Arduino Microcontroller Processing for Everyone*, S. Barrett, 3rd ed., Morgan & Claypool Publishers, San Rafael, CA, 2013.

ded system developers will find a seamless transition between the MSP430 and MSP432 line of processors.

Chapter 3 introduces the MSP430 hardware architecture, software organization, and programming model. The chapter also presents an introduction to the MSP430 orthogonal instruction set, including its 27 instructions and 9 emulated instructions.

Chapter 4 describes a wide variety of input and output devices and how to properly interface them to the MSP430 microcontroller. We believe it is essential for the embedded system designer to understand the electrical characteristics of the processor so a proper interface to peripheral components may be designed. We have included a chapter on these concepts for the books we have written for the Synthesis Lecture Series. We continue to add material as new microcontroller peripherals are developed. The chapter begins with a review of the MSP430 electrical operating parameters followed by a discussion of the port system. The chapter includes a description of a wide variety of input device concepts including switches, interfacing, debouncing, and sensors. Output device concepts are then discussed including light-emitting diodes (LEDs), tri–state LED indicators, liquid crystal displays (LCDs), high-power DC and AC devices, motors, and annunciator devices.

Chapter 5 provides an in-depth discussion of the MSP430 power management system. The power management system provides for ultra-low power operation and practices.

Chapter 6 is dedicated to the different memory components onboard the MSP430 including the new FRAM nonvolatile memory, RAM, EEPROM and the associated memory controllers. The Direct Memory Access (DMA) controller is also discussed.

Chapter 7 discusses the clock and timer systems aboard the MSP430. The chapter begins with a detailed discussion of the flexible clock system, followed by a discussion of the timer system architecture. The timer architecture discussion includes the Watchdog timers, timers A and B, real-time clocks, and pulse width modulation (PWM).

Chapter 8 provides an introduction to the concepts of resets and interrupts. The various interrupt systems associated with the MSP430 are discussed, followed by detailed instructions on how to properly configure and program them.

Chapter 9 discusses the analog systems aboard the MSP430. The chapter discusses the analog-to-digital converters (ADCs), the digital-to-analog converters (DACs), and the comparators.

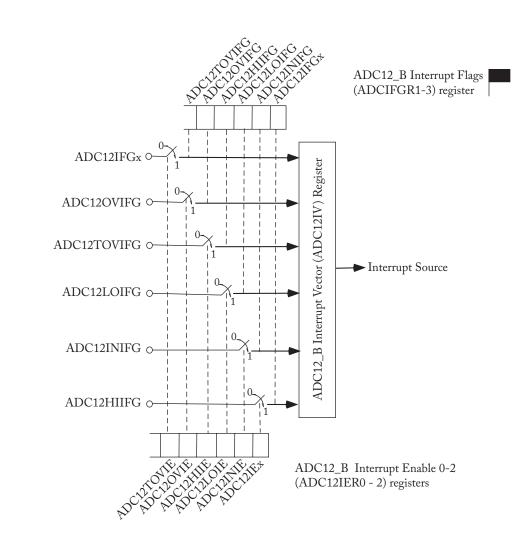

Chapter 10 is designed for a detailed review of the complement of serial communication systems resident onboard the MSP430, including the universal asynchronous receiver transmitter (UART), the serial peripheral interface (SPI), the I2C system, the radio frequency (RF) link, USB, and the IrDA infrared link. The systems are contained within the MSP430 universal serial communication interfaces eUSCI\_A and eUSCI\_B subsystems.

Chapter 11 provides a detailed introduction to the data integrity features aboard the MSP430 including a discussion of noise and its sources and suppression, an Advanced Encryption Standard (AES) 256 accelerator module, and a 16- or 32-bit cyclic redundancy check

#### xxvi PREFACE

(CRC) engine. This chapter was adapted from material originally written for the Texas Instruments MSP432, a 32-bit processor that has close ties to the 16-bit MSP430.<sup>2</sup> Embedded system developers will find a seamless transition between the MSP430 and MSP432 line of processors.

Chapter 12 discusses the system design process followed by system level examples. We view the microcontroller as the key component within the larger host system. It is essential the embedded system designer has development, design, and project management skills to successfully complete a project. This chapter provides an introduction some of the skills used for project development. We have included a chapter on these concepts for the books we have written for the Synthesis Lecture Series. The examples have been carefully chosen to employ a wide variety of MSP430 systems discussed throughout the book.

Table 1 provides a summary of chapter contents and related MSP430 subsystems.

Steven F. Barrett and Daniel J. Pack July 2019

<sup>2</sup>Embedded Systems Design with the Texas Instruments MSP432 32-bit Processor, Dung Dang, Daniel J. Pack, and Steven F. Barrett, Morgan & Claypool Publishers, San Rafael, CA, 2017.

| Chapter                      | MSP- EXP430FR2433               | MSP-EXP430FR5994                 |

|------------------------------|---------------------------------|----------------------------------|

| Ch. 1: Introduction          |                                 |                                  |

| Ch. 2: Programming           | MSP430 port system              | MSP430 port system               |

| Ch. 3: HW and SW             | Joint Test Action Group (JTAG)  | Joint Test Action Group (JTAG)   |

|                              | serial debug port, Enhanced     | serial debug port, Enhanced      |

|                              | Emulation Module (EEM) onboard  | Emulation Module (EEM) on-       |

|                              | debug tool, serial Spy-Bi-Wire  | board debug tool, serial Spy-Bi- |

|                              | (SBY) JTAG                      | Wire (SBY) JTAG                  |

| Ch. 4: Interfacing           | MSP430 port system              | MSP430 port system               |

| Ch. 5: Power Mgt             | Power Mgt Module                | Power Mgt: LDO, SVS,             |

|                              |                                 | Brownout                         |

| Ch. 6: Memory                | FRAM: 15KB + 512B               | FRAM: 256KB                      |

| 2                            | RAM: 4KB                        | RAM: 4 KB + 4 KB                 |

|                              |                                 | DMA Controller                   |

|                              |                                 | Memory Protection Unit (MPU)     |

|                              |                                 | IP Encapsulation Segment (IPE)   |

| Ch. 7: Timer Systems         | Clock system (CS), LFXT         | Clock system (CS),               |

| - Clock                      | Timer_A3(2), Timer_A2(2)        | TB0: Timer_B, TA0: Timer_A       |

| - Timers                     | Watchdog, Real-Time Clock       | TA1: Timer_A, TA4: Timer_A       |

|                              |                                 | Watchdog, Real-Time Clock        |

| Ch. 8: Resets and Interrupts |                                 |                                  |

| Ch. 9: Analog Peripherals    | ADC: 8 ch, SE, 10-bit, 200 ksps | Comp_E: 16 ch, Ref_A             |

|                              | -                               | ADC 12_B: 16 ch SE/8 DE, 12-bi   |

| Ch. 10: Comm Sys             | eUSCI_A(2)                      | eUSCI_A(4) (A0 to A3)            |

|                              | - UART, IrDA, SPI               | - UART, IrDA, SPI                |

|                              | eUSCI_B0                        | eUSCI_B(4) (B0 to B3)            |

|                              | - SPI, I2C                      | - SPI, I2C                       |

| Ch. 11: System Integrity     | CRC16: 16-bit cyclic redun-     | CRC16: CRC-16-CCITT              |

| /                            | dancy check                     | CRC32: CRC-32-ISO-3309           |

|                              |                                 | AES 256: security encryption.    |

|                              |                                 | decryption                       |

| Ch. 12: System Design        |                                 |                                  |

## Table 1: MSP-EXP430FR5994 and the MSP-EXP430FR2433 LaunchPad subsystems.

# Acknowledgments

There have been many people involved in the conception and production of this book. We especially want to thank Doug Phillips, Mark Easley, and Franklin Cooper of Texas Instruments. The future of Texas Instruments is bright with such helpful, dedicated engineering and staff members. In 2005, Joel Claypool of Morgan & Claypool Publishers, invited us to write a book on microcontrollers for his new series titled "Synthesis Lectures on Digital Circuits and Systems." The result was the book Microcontrollers Fundamentals for Engineers and Scientists. Since then we have been regular contributors to the series. Our goal has been to provide the fundamental concepts common to all microcontrollers and then apply the concepts to the specific microcontroller under discussion. We believe that once you have mastered these fundamental concepts, they are easily transportable to different processors. As with many other projects, he has provided his publishing expertise to convert our final draft into a finished product. We thank him for his support on this project and many others. He has provided many novice writers the opportunity to become published authors. His vision and expertise in the publishing world made this book possible. We thank Sara Kreisman of Rambling Rose Press, Inc. for her editorial expertise. We also thank Dr. C.L. Tondo of T&T TechWorks, Inc. and his staff for working their magic to convert our final draft into a beautiful book. Finally, we thank our families who have provided their ongoing support and understanding while we worked on books over the past fifteen plus years.

Steven F. Barrett and Daniel J. Pack July 2019

## CHAPTER 1

# Introduction to Microcontroller Technology

**Objectives:** After reading this chapter, the reader should be able to:

- describe the key technological accomplishments leading to the development of the microcontroller;

- define microprocessor, microcontroller, and microcomputer;

- identify examples of microcontroller applications in daily life;

- list key attributes of the MSP430 microcontroller;

- describe different features that differentiate MSP430 microcontroller family members;

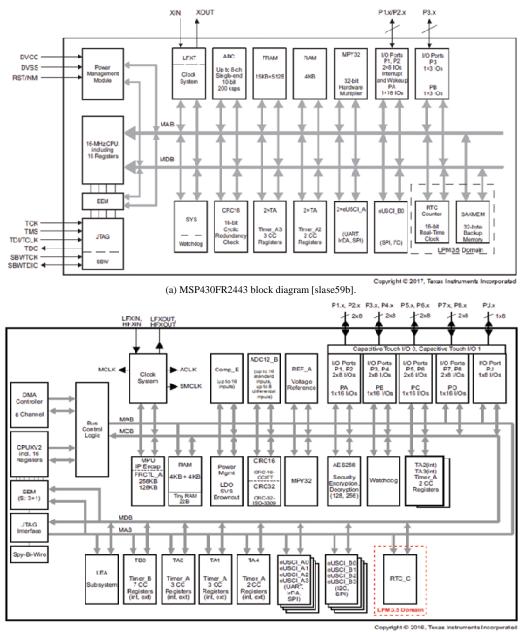

- list the subsystems onboard the MSP430FR2433 and the MSP430FR5994 microcontrollers;

- provide an example application for each subsystem onboard the MSP430 microcontrollers;

- describe the hardware, software, and emulation tools available for the MSP430 microcontrollers; and

- employ the development tools to load and execute simple programs on the MSP-EXP430FR2433 and the MSP-EXP430FR5994 evaluation boards.

In every chapter, we start with a motivation and background followed by a section on theory. After the theory section, an example application is used to demonstrate the operational use of chapter concepts. Each chapter includes a hands-on laboratory exercise and a list of chapter references, which you can use to explore further areas of interest. Each chapter concludes with a series of practice exercises, divided into Fundamental, Advanced, and Challenging levels.

## 1.1 MOTIVATION

This book is about microcontrollers! A microcontroller is a self-contained processor system in a single integrated circuit (IC or chip) that contains essential functional units of a general-purpose computer such as a central processing unit (CPU), a memory, and input/output (I/O) units.

#### 2 1. INTRODUCTION TO MICROCONTROLLER TECHNOLOGY

Microcontrollers provide local computational resources to many products, requiring a limited amount of processing power to perform their functions. They are everywhere! In the routine of daily life, we use multiple microcontrollers. Take a few minutes and jot down a list of microcontroller equipped products, sometimes called embedded systems, you have used today.

This chapter introduces the Texas Instruments MSP430 line of microcontrollers. We begin with a brief history of computer technology followed by an introduction to the MSP430FR2433 and the MSP430FR5994 microcontrollers. After a review of these MSP430 microcontrollers, we introduce you to the powerful and user-friendly development tools.

## 1.2 BACKGROUND THEORY: A BRIEF HISTORY AND TERMINOLOGY

The development of microcontrollers can be traced back to the time of early computing with the first generation of computers. The generations of computer development are marked by break-throughs in hardware and architecture innovation. The first generation of computers employed vacuum tubes as the main switching element. Mauchly and Eckert developed the electronic numerical integrator and calculator (ENIAC) in the mid 1940s. This computer was large and consumed considerable power due to its use of 18,000 vacuum tubes. The computer, funded by the U.S. Army, was employed to calculate ordnance trajectories in World War II. The first commercially available computer of this era was the UNIVAC I [Bartee, 1972].

The second generation of computers employed transistors as the main switching element. The transistor was developed in 1947 by John Bardeen and Walter Brattain at Bell Telephone Laboratories. Bardeen, Brattain, and William Schockley were awarded the 1956 Nobel Prize in Physics for development of the transistor [Nobel.org]. The transistor reduced the cost, size, and power consumption of computers.

The third generation of processors started with the development of the integrated circuit. The integrated circuit was developed by Jack Kilby at Texas Instruments in 1958. The integrated circuit revolutionized the production of computers, greatly reducing their size and power consumption. Computers employing integrated circuits were first launched in 1965 [Bartee, 1972], and Kilby was awarded the Nobel Prize in Physics in 2002 for his work on the integrated circuit [Nobel.org]. The first commercially available minicomputer of this generation was the digital equipment corporation's (DEC) PDP-8 [Osborne, 1980].

The fourth generation of computers was marked by the advancement of levels of integration, leading to very large-scale integration (VLSI) and ultra-large scale integration (ULSI) production techniques. In 1969, the Data Point Corporation of San Antonio, Texas had designed an elementary CPU. The CPU provides the arithmetic and control for a computer. Data Point contracted with Intel and Texas Instruments to place the design on a single integrated circuit. Intel was able to complete the task, but Data Point rejected the processor as being too slow for their intended application [Osborne, 1980].

#### 1.3. MICROCONTROLLER SYSTEMS 3

Intel used the project as the basis for their first general-purpose 8-bit microprocessor, the Intel 8008. The microprocessor chip housed the arithmetic and control unit for the computer. Other related components such as memory (ROM), random access memory (RAM), I/O components, and interface hardware were contained in external chips. From 1971–1977, Intel released the 8008, 8080, and 8085 microprocessors which significantly reduced the number of system components and improved upon the number of power supply voltages required for the chips. Some of the high visibility products of this generation were the Apple II personal computer, developed by Steve Jobs and Steve Wozniak and released in 1977, and the IBM personal computer, released in 1981 [MCS 85, 1977, Osborne, 1980].

The first single-chip microcontroller was developed by Gary Boone of Texas Instruments in the early 1970s. A microcontroller contains all key elements of a computer system within a single integrated circuit. Boone's first microcontroller, the TMS 1000, contained the CPU, ROM, RAM, and I/O and featured a 400 kHz clock [Boone, 1973, 1978]. From this early launch of microcontrollers, an entire industry was launched. There are now over 35 plus companies manufacturing microcontrollers worldwide offering over 250 different product lines [Wendt]. The MSP430 line of microcontrollers was first developed in 1992 and became available for worldwide release in 1997.

## **1.3 MICROCONTROLLER SYSTEMS**

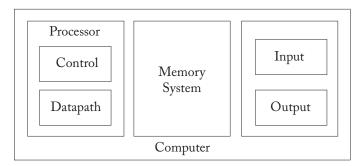

Although today's microcontrollers physically bear no resemblance to their earlier computer predecessors, they all have a similar architecture. All computers share the basic systems shown in Figure 1.1. The processor or CPU contains both datapath and control hardware. The datapath is often referred to as the arithmetic logic unit (ALU). As its name implies, the ALU provides hardware to perform the mathematical and logic operations for the computer. The control unit provides an interface between the computer's hardware and software. It generates control signals to the datapath and other system components such that operations occur in the correct order and within an appropriate time to execute the desired actions of a software program.

Figure 1.1: Basic computer architecture. (Adapted from Patterson and Hennessy [1994].)

#### 4 1. INTRODUCTION TO MICROCONTROLLER TECHNOLOGY

The memory system contains a variety of memory components to support the operation of the computer. Typical memory systems aboard microcontrollers contain RAM, ROM, and electrically erasable programmable read only memory (EEPROM) components. RAM is volatile. When power is unavailable, the contents of RAM memory is lost. RAM is typically used in microcontroller operations for storing global variables, local variables, which are required during execution of a function, and to support heap operations during dynamic allocation activities. In contrast, ROM memory is nonvolatile. That is, it retains its contents even when power is not available. ROM memory is used to store system constants and parameters. If a microcontroller application is going to be mass produced, the resident application program may also be written into ROM memory at the manufacturer.

EEPROM is available in two variants: byte-addressable and flash programmable. Byteaddressable memory EEPROM, as its name implies, allows variables to be stored, read, and written during program execution. The access time for byte-addressable EEPROM is much slower than RAM memory; however, when power is lost, the EEPROM memory retains its contents. Byte-addressable EEPROM may be used to store system passwords and constants. For example, if a microcontroller-based algorithm has been developed to control the operation of a wide range of industrial doors, system constants for a specific door type can be programmed into the microcontroller onsite when the door is installed. Flash EEPROM can be erased or programmed in bulk. It is typically used to store an entire program.

Ferroelectric Random Access Memory (FRAM) is a nonvolatile, ultra-low power (ULP) with access speeds similar to RAM. It has been termed a universal memory because it can be used for storing program code, variables, constants, and for stack operations. Note these functions are typically performed by nonvolatile ROM and volatile RAM. FRAM also has a high level of write endurance on the order of 10<sup>15</sup> cycles [SLAA526A, 2014, SLAA628, 2014].

The input and output system of a microcontroller usually consists of a complement of ports. Ports are fixed sized hardware registers that allow for the orderly transfer of data in and out of the microcontroller. In most microcontroller systems, ports are equipped for dual use. That is, they may be used for general-purpose digital I/O operations or may have alternate functions such as input access for the analog-to-digital (ADC) system.

Our discussion thus far has been about microcontrollers in general. For the remainder of this chapter and the rest of the book, we concentrate on the Texas Instruments MSP430 microcontroller, specifically the MSP430FR2433 and the MSP430FR5994.

### 1.4 WHY THE TEXAS INSTRUMENTS MSP430?

The MSP430 line of microcontrollers began development in 1992. Since this initial start, there have been multiple families of the microcontroller developed and produced with a wide range of features. This allows one to choose an appropriate microcontroller for a specific application. Texas Instruments invests considerable resources in providing support documentation, development tools, and instructional aids for this processor family.

### 1.5. TARGET MICROCONTROLLER FEATURES 5

The various families of the MSP430 have the following traits [SLAB034AD, 2017]:

- low-power supply range,

- ultra-low power (ULP) consumption,

- 16-bit reduced instruction set (RISC) architecture,

- over 300 code compatible products,

- capability to integrate digital and analog components,

- compatible radio frequency (RF) peripheral components to provide wireless communications,

- onboard ADC and digital-to-analog converter (DAC) system, and

- full range of documentation and support for the student, design engineer, and instructor.

## **1.5 TARGET MICROCONTROLLER FEATURES**

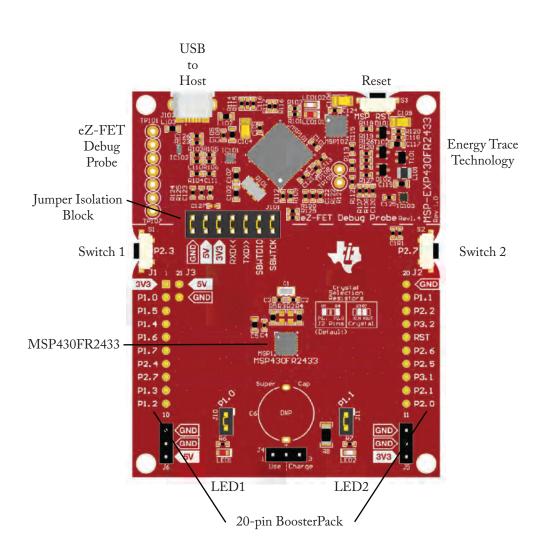

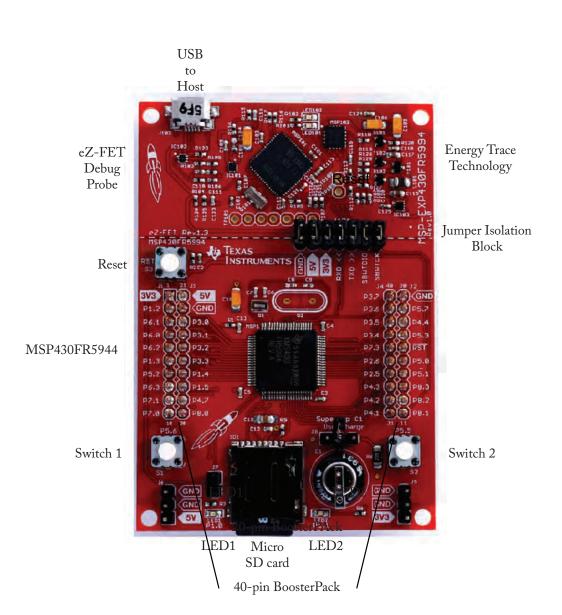

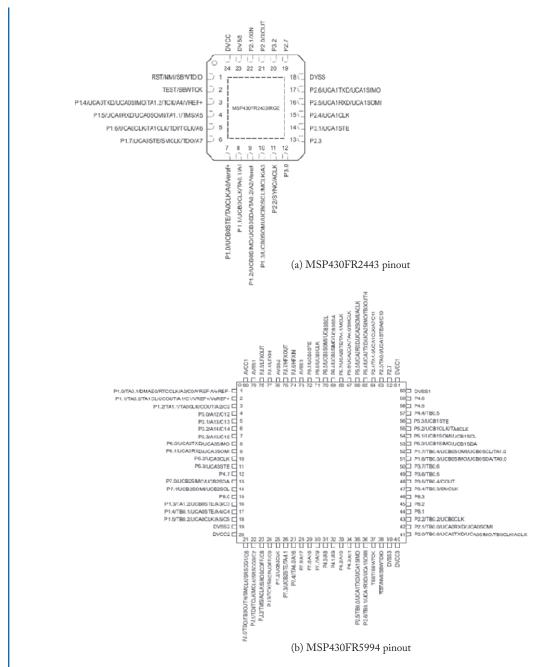

Figure 1.2 provides a summary of features for the MS430-EXPFR2433 (FR2433) and the MSP-EXP430FR5994 (FR5994) evaluation modules (EVM). We discuss features common to both, followed by features specific to the FR5994.

The FR2433 and FR5994 possess the following common features [SLAB034AD, 2017, SLASE59D, 2018, SLASE54C, 2018]:

- operating frequency up to 16 MHz,

- 16-bit RISC architecture,

- low supply voltage range: 1.8–3.6 VDC,

- ULP consumption,

- brown-out reset,

- large complement of general-purpose I/O pins,

- multi-channel, high-resolution analog-to-digital converter,

- hardware multiplier,

- multiple enhanced universal serial communication interfaces (eUSCI),

- multiple basic timers,

- memory system including FRAM for program and data memory and SRAM,

| MSP-EXP430FR2433<br>Evaluation Module (EVM)<br>FR2xx/FR4xx family | MSP-EXP430FR5994<br>Evaluation Module (EVM)<br>FRxx FRAM Family |

|-------------------------------------------------------------------|-----------------------------------------------------------------|

| - Speed: 16 MHz                                                   | - Speed: 16 MHz                                                 |

| - Voltage: 1.8–3.6 VDC                                            | - Voltage 1.8–3.6 VDC                                           |

| - Ports                                                           | - Ports                                                         |

| - PA(16), PB(3)                                                   | - PA(16), PB(16), PC(16)<br>PD(16), PJ(8)                       |

| - ADC 10-bit, 8-channel                                           | - ADC 12-bit, 16-channel                                        |

| conversion                                                        | conversion                                                      |

| - Hardware multiplier                                             | - Hardware multiplier                                           |

| (MPY), 32 bit                                                     | (MPY), 32 bit                                                   |

| - Universal serial comm                                           | - Universal serial comm                                         |

| interface (eUSCI)(3)                                              | interface (eUSCI)(8)                                            |

| - A0, A1:                                                         | - A0, A1, A2, A3:                                               |

| - UART, IrDA, SPI                                                 | - UART, IrDA, SPI                                               |

| - B0:                                                             | - B0, B1, B2, B3:                                               |

| - I2C, SPI                                                        | - I2C, SPI                                                      |

| - Basic timer                                                     | - Basic timer (4)                                               |

| - Timer_A2 (2)                                                    | - TA0, 1, 4                                                     |

| - Timer_A3 (2)                                                    | - TB0                                                           |

| - Memory:                                                         | - Memory:                                                       |

| - FRAM: 15.5 KB                                                   | - FRAM: 256 KB                                                  |

| - 15K program                                                     | <ul> <li>flexible configuration</li> </ul>                      |

| - 512 B data                                                      | - xxxK program                                                  |

| - 4 KB SRAM                                                       | - xxxB info                                                     |

|                                                                   | - 8 KB SRAM                                                     |

| - Power Mgt Module (PMM)                                          | - Supply voltage<br>supervisor (SVS)                            |

| - Clock System (CS) and                                           | - Clock System (CS) and                                         |

| distribution                                                      | distribution                                                    |

| - Cyclic Redundancy                                               | - Cyclic Redundancy                                             |

| Check (CRC), 16-bit                                               | Check (CRC), 16- or 32-bit                                      |

| - Embedded Emulation                                              | - Embedded Emulation                                            |

| Module (EEM)                                                      | Module (EEM)                                                    |

| - Watch dog timer, 16-bit                                         | - Watch dog timer                                               |

| - Real-time Clock, 16-bit                                         | - Real-time Clock                                               |

| - JTAG                                                            | - JTAG                                                          |

| - Spy-Bi-Wire (SBW)                                               | - Spy-Bi-Wire (SBW)                                             |

| -1)                                                               | - Analog comparator                                             |

|                                                                   | (Comp_A), 16-channel                                            |

|                                                                   | - Direct memory                                                 |

|                                                                   | access (DMA), 6-channel                                         |

|                                                                   | - Onboard LCD controller                                        |

|                                                                   | - Capacitive touch                                              |

|                                                                   | - Hardware encryption                                           |

|                                                                   | (AES), 128- or 256-bit                                          |

Figure 1.2: MSP430 features [SLAB034AD, 2017, SLASE59D, 2018, SLASE54C, 2018].

#### 1.5. TARGET MICROCONTROLLER FEATURES 7

- power management features,

- flexible clock system (CS),

- cyclic redundancy check (CRC),

- embedded emulation module (EEM),

- watch dog timer (WDT),

- real-time clock (RTC),

- joint test action group (JTAG) interface,

- spy-bi-wire (SBW) JTAG interface,

- onboard light crystal display (LCD) controller (FR5994), and

- low-energy accelerator (LEA) (FR5994).

In addition, the MSP-EXP430FR5994 EVM has the following features:

- analog comparators,

- six channels of internal direct memory access (DMA),

- onboard LCD controller,

- · capacitive touch features, and

- hardware AES encryption.

Provided below is a brief summary of these features. More details are found throughout the remainder of the book [SLAB034AD, 2017, SLASE59D, 2018, SLASE54C, 2018]:

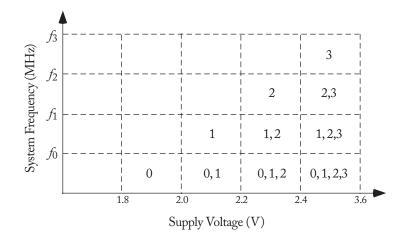

**Maximum operating frequency: 16 MHz.** Both the FR2433 and the FR5994 EVMs have a maximum operating frequency of 16 MHz. Generally speaking, a microcontroller's power consumption is linearly related to its operating frequency. Microcontrollers are typically used in remote applications sourced by battery power. To conserve energy the microcontroller is placed in low-power, low-frequency sleep mode when inactive. The microcontroller is awoken when needed. Therefore, a microcontroller needs a combination of both high- and low-frequency clock sources, different operating modes, and the ability to quickly transition between the modes. The MSP430 is equipped with a flexible and stable clock and distribution system to satisfy these requirements.

**16-bit RISC architecture.** Reduced instruction set computer (RISC) architecture is based on the premise of designing a processor that is very efficient in executing a basic set of building

block instructions. From this set of basic instructions more complex instructions may be constructed. The 16-bit data width establishes the range of numerical arguments that may be used within the processor. For example, a 16-bit processor can easily handle 16-bit unsigned integers. This provides a range of unsigned integer arguments from 0 to  $(2^{16} - 1)$  or approximately 65,535. Larger arguments may be handled, but additional software manipulation is required for processing, which consumes precious execution time.

Low supply voltage range: 1.8–3.6 VDC. The MSP430 operates at very low voltages. Some operating voltage of interest include:

- 3.6 V: close to Li-ion battery supply range (rechargeable electronic battery);

- 1.8–3.6 V: 2x AA or AAA batteries, coin-cell applications, and energy harvesting applications. In energy harvesting techniques, energy is derived from sources external to the microcontroller; and

- 1.8 V: many modern sensors/consumer electronics operate at 1.8 V. Being able to run the microcontroller at this range means the whole system can operate at VCC = 1.8 V.

**Ultra-low power consumption.** The MSP430 has a variety of operating modes including an active mode (AM) and multiple low-power modes (LPM). In the active mode, the MSP430 draws 126 (FR2433)/118 (FR5994) microamps of current per MHz of clock speed. In the standby mode the MSP430 draws less than one microamp of current. In LPM 3.5 and operating from a RTC frequency of 32,768 Hz, the MSP430 draws 73 nA (FR2433) and 350 nA (FR5994). In LPM 4.5 shutdown mode, the MSP430 draws 16 nA (FR2433) and 45 nA (FR5994) of current [SLASE59D, 2018, SLASE54C, 2018].

Large complement of I/O ports. The FR2433 is equipped with a single 16-bit digital I/O port, designated as PA. This port may also be subdivided into two 8-bit ports, designated as P1 and P2. The FR2433 also has a 3-bit, port designated as PB. The FR5994 is equipped with a four 16-bit digital I/O ports, designated as PA through PD. These ports may also be subdivided into two 8-bit ports. For example, port PA may be as designated P1 and P2. The FR5994 also has an 8-bit port, designated as PJ.

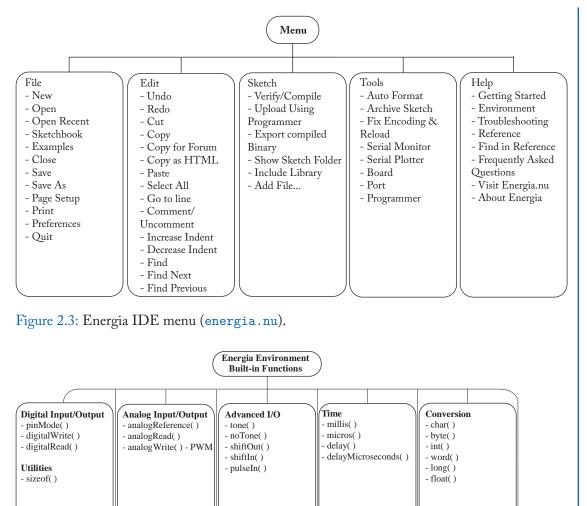

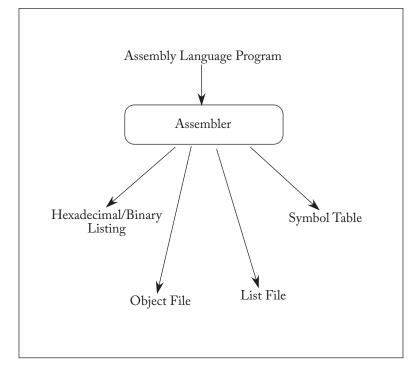

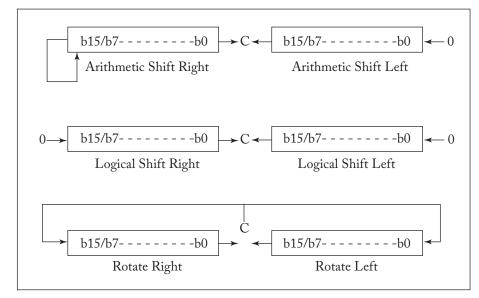

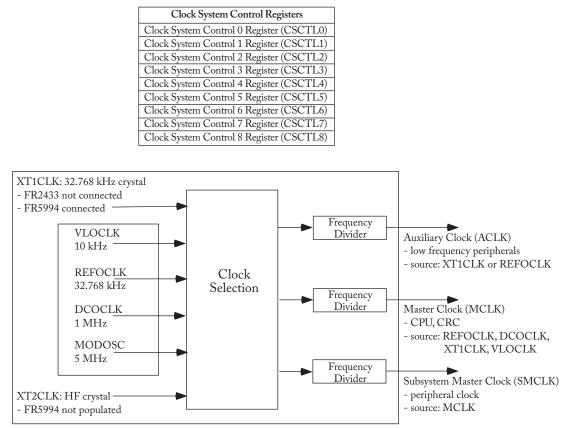

**Multi-channel, high-resolution analog-to-digital converter.** The FR2433 is equipped with an 8-channel, 10-bit analog-to-digital converter. The FR5994 is equipped with 16 channels of 12-bit ADC. This feature provides for a large number of converters and very good resolution of analog signals converted.